依照依据Windows的言语(C、C++、C#)等编程言语的初学入门教程,第一个进程应该是“Hello World!”的例程。但由于硬件上的驱动难易程度,此例程将在在后续规章中推出。硬件工程师学习开发板的第一个例程:流水灯,全部夸姣的开端。

本章将会在规划代码的一起,解说Quartus II 软件的运用,后续章节中只讲软件的思维,以及解决方案,不再做过多的负担描绘。

一、Step By Step 树立第一个工程

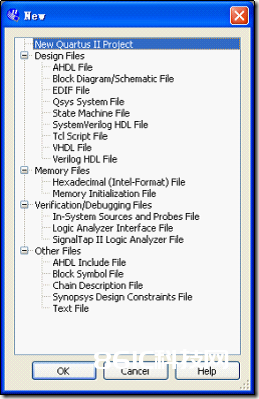

(1)树立第一个工程,File-New-New Quartus II Project,如下图所示,OK。

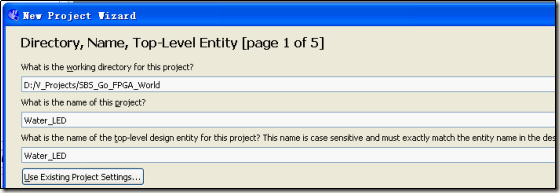

(2)Next,如下图所示,挑选工程目录(不能有空格,中文途径),一起输入工程名与顶层文件名。

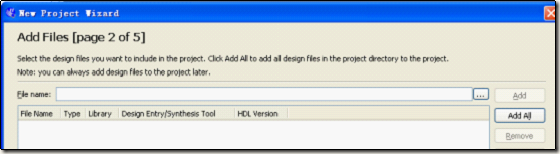

(3)若有现成的代码,能够直接挑选添参加工程;不然,直接next,进入下一步,如下图所示:

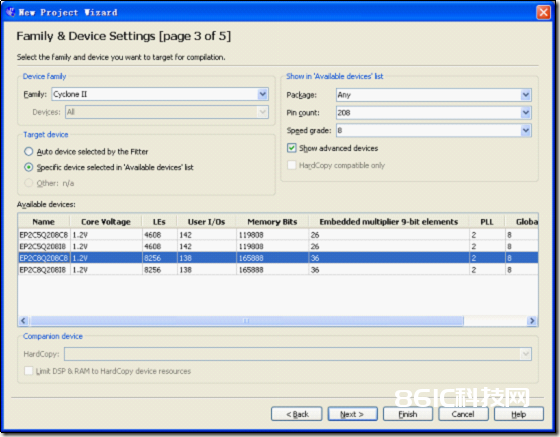

(4)依据自己的硬件设备,挑选相应的设备方针器材。

(5)Next,Finish。

二、工程代码规划

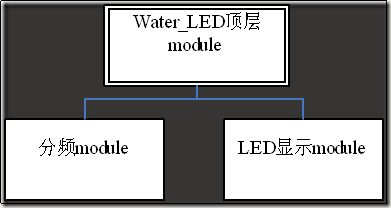

1. water_led_design工程文件结构:

如上图所示,工程分为三个模块,分别为:

(1)顶层模块 : 例化各个模块,工程的最高级别文件。

(2)分频模块 : 经过分频得到固定的频率(10Hz)。

(3)LED显现模块: 随固定频率,来操作LED灯。

2. 代码规划

(1)warter_led.v模块规划

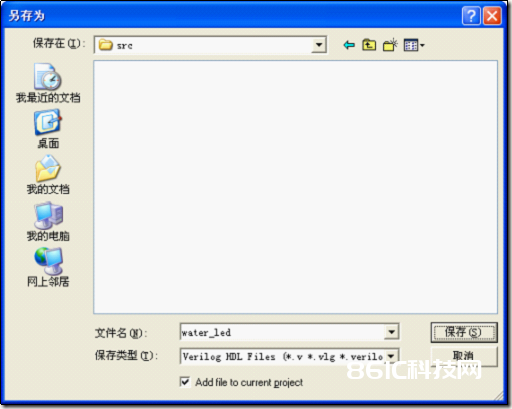

a) New-File,新建verilog文件,保存于新建在工程目录下的src文件夹中(仅仅为了工程文件结构安排的明晰,更长于办理)。如下图所示:

b) 输入代码,界说输入输出接口,如下所示:

module water_led

(

input clk, //global clock 50MHz

input rst_n, //global clock reset

output [5:0] led_data //user led interface

);

endmodule