0 导言

跟着卫星通信速率的不断进步,高速数字调制技能得到了快速的开展,而因为后端电路及放大器的非线性,假如码率与中频的相对带宽较高,则会构成通带内频谱特性的不平整。因而,跟着码元速率的进步,中频也得相应地进步以取得更好的调制信号质量。因为中频的进步,导致了DAC采样率的进步。本文探讨了DAC在欠采样下组成高中频信号的办法,规划了对单个不甚高速的DAC,通过后端电路处理,在采样率低于奈奎斯特率的状况下,直接组成第二奈奎斯特域的高中频信号的计划。最终,对组成的信号进行了频谱剖析及补偿,而且给出仿真与试验成果。

1 欠采样DAC组成高中频信号

关于高中频调制,其间一个规划难点就是DAC的高采样率问题。关于中频1800MHz,带宽960MHz的高中频信号,假如DAC选用奈奎斯特率采样而且考虑后端滤波器,则需求采样率达5.7GHz以上的DAC,这对DAC内部的采样电路有着很高的要求,而且会添加体系复杂度。

咱们知道,DAC完结一次数模转化的最小时刻为DAC的树立时刻,为了确保数模转化的正确性,有必要确保DAC的树立时刻小于DAC的采样率。因而,关于高采样率的DAC,首先得减小DAC的树立时刻。树立时刻是由DAC内部电子开关的动作时刻和运算放大器的输出电压时刻所决议。所以高采样率的DAC关于内部物理器材功能的要求很高,这就使得高采样率的DAC产品比较贵重。而市面上采样率很高的DAC也比较少,所以使用较低速率的DAC组成超奈奎斯特域的高频信号就显得尤为重要。

现在使用低于奈奎斯特采样率的DAC组成高中频信号的办法有两种:

(1)使用两个DAC输出的组成转化,等效地进步DAC的采样率,如文献中把两个DAC交织接入一个单元,混频器用作开关,能够有效地使全体采样速率添加一倍。轮番更新每个DAC,并切换到这种办法使得总的采样率从单个DAC的fs等效进步为2fs。可是这种办法受限于乘法器的速度,所以不适用于采样率很高的状况。

(2)使用低于奈奎斯特采样率的DAC对高中频信号进行欠采样,再使用第二乃至第三奈奎斯特域的频谱进行高频信号的直接组成。

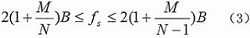

令信号的最低频率为fL,最高频率为fH,fH=NB+MB,其间N为不超越fH(fH-fL)的最大整数。为了确保带通信号的频谱镜像之间不混叠,采样频率应该大于信号带宽的两倍,而且满意以下条件:

Nfs-fH>fH (1)

Nfs-fL

故采样频率应该满意:

在欠采样时,当采样率满意式(3),便能够完成高频信号在超奈奎斯特域的组成。本规划中,中频为1800MHz,中频信号带宽为960MHz,所以有fL=1320MHz,fH=2280MHz,则N=2,M=0.376,2280

第二种办法比较于榜首种办法只使用了一个DAC,节省了DAC芯片资源,可是因为超奈奎斯特域的镜像频谱相关于奈奎斯特域里的信号频谱重量会有比较大的衰减,所以构成频谱补偿的困难。本规划通过后端电路的处理,加强了超奈奎斯特域的信号强度,在优化第二种办法的基础上完成了第二奈奎斯特域的高中频信号的直接组成。

2 本规划的计划

2.1 计划概述

本规划运用了欠采样第二种办法比较于榜首种办法只使用了一个DAC完成第二奈奎斯特域高中频信号组成的思维,并在其基础上做了改善。因为第二种办法比较于榜首种办法只使用了一个DAC的数模转化进程是在采样时钟的操控下进行的。每到采样时钟的上升沿第二种办法比较于榜首种办法只使用了一个DAC就开端新的转化,为了能用较低采样率的第二种办法比较于榜首种办法只使用了一个DAC组成超奈奎斯特域的信号,咱们需求使用后端电路加强信号的高频成分,以到达更好的高频信号组成质量。

本规划的完成框图如图1所示。

其间PLL发生的CLK1为DAC的采样时钟,CLK2为高速电子开关的时钟,其间CLK2是CLK1的倍频,高中频通过DAC采样后,发生两路信号,其间一路是DAC输出信号的反相电平输出,另一路是DAC输出信号的延时,这两路信号在被CLK2驱动的高速电子开关的效果下,完成了一个周期内信号的双相电平输出。这种输出办法会带来频谱的歪曲,因而需求在数据进入DAC之前进行补偿,详细补偿计划在本节的后半部分评论。

其间,DAC输出的信号时域图如图2所示。

在高速电子开关效果下的输出信号为:

通过图3咱们能够看出,在一个DAC采样时钟的前半个周期内输出了采样数据的正的幅值,而在后半个周期内输出采样数据的负的幅值,这样能更好地加强信号的高频成份。

2. 2 输出信号频谱剖析及补偿计划

因为DAC的零阶抽样坚持效应,会在通带内构成sinc包络,DAC输出信号的包络与通过开关挑选后输出的信号包络如图4所示。

由图4咱们看到,DAC输出信号的包络在3/4fs处衰减了10dB,而且关于3/4fs左右不对称,在高中频地点的第二奈奎斯特域里衰减严峻。在高速电子开关效果下的双相位形式中,第二奈奎斯特域的频率重量被加强了,由DAC阶梯效应构成的信号包络的峰值在第二奈奎斯特域中,当fs为2400MHz时,1800MHz的高中频处于sinc包络的峰值处,包络关于3/4fs两头近似对称,而且在第二奈奎斯特域中频谱特性较为平整。此刻,因为半周期内信号起伏的倒转与坚持效应发生的如图4所示的sinc包络,需求在DAC之前引进具有如下补偿特性的滤波器,对进行数模转化的信号预处理。滤波器的频响特性为:

考虑到后端的带通滤波器,调制信号带宽最大为0.4*fs=960MHz,咱们只关怀带内的补偿即可。用Matlab生成的DAC之前的反sinc滤波器的频谱起伏为图5所示。

本规划只使用了一个DAC进行高中频信号的组成,减少了DAC芯片资源的耗费,而且通过加强第二奈奎斯特域频率重量的办法,能够下降补偿的困难,进步组成信号的质量,具有有用含义。

因为本规划的方针是完成中频1800MHz,带宽为960MHz的高中频信号,依据剖析,规划了DAC的后端电路,完成信号一个采样周期内的双相位输出,用采样率为2400MHz的DAC完成了第二奈奎斯特域的高中频信号的直接组成。关于不同的需求,可能有不同的办法挑选,而事实上,还能通过开关电路完成归零码或许调理输出的不同占空比,来习惯特别环境下的需求,这点在文献中有阐明。

3 仿真与试验成果剖析

本规划选用QPSK调制,码元速率为710MSPS,通过星座图映射,0.35成形,插值后的I、Q两路基带信号带宽为480MHz,与数字NCO发生的1800MHz的数字载波相乘,构成中频1800MHz,带宽960MHz的已调信号,采样率为2400MHz。

本规划的Simulink仿真模型如下:

图6中的scope1显现的4路信号分别是两路正交数字载波与通过成形插值后的I、Q两路基带信号,scope1中的4路信号如图7所示。

图8是图6中scope显现的3路信号。

其间榜首路为DAC正相输出的时域波形,第二路为DAC反相输出的时域波形,第三路是通过高速开关之后的信号时域波形。由图8咱们能够看出,在开关效果下、每个DAC采样时钟周期输出了正反两个相位的信号。如图6所示,开关挑选后的输出信号通过7阶的巴特沃斯带通滤波器后,能够得到第二奈奎斯特域的中频为1800MHz,带宽为960MHz的信号如图9所示。

用低通滤波器滤出的前两个奈奎斯特域的信号如图10所示。

由图10能够看出,因为DAC作业在欠采样率下,存在600MHz与1800MHz两个中频的调制信号;别的,本规划使用高速开关与DAC后端电路及前端补偿,在一周期内完成信号双相输出的计划,有效地加强了第二奈奎斯特域的频率重量。图10中,因为存在两个频率重量,故时域波形表现为两种中频频率的调制信号的叠加,而图9带通滤波后,时域波形是第二奈奎斯特域的高中频调制信号。

4 定论

本文探讨了一种使用低于奈奎斯特采样率的DAC及其后端电路,完成第二奈奎斯特域的高中频直接组成的办法,给出了全体规划计划、频谱剖析并提出补偿计划。在QPSK的调制形式下,进行了高中频调制信号通过本规划的DAC及其后端电路的仿真,仿真成果证明,本计划能加强第二奈奎斯特域的频谱重量,下降补偿的困难,进步组成信号的质量,在DAC的采样率低于奈奎斯特率的状况下,完成高中频信号的直接组成。