CRC基本原理

在串行数据流的最有用的检错计划是CRC(Cyclic Redundancy check)循环冗余查验,CRC循环冗余校验最底子的原理便是将原始数据除以某个固定的数,然后所得的余数便是CRC校验码,依据校验码位数的不同常用的CRC循环冗余校验算法有:CRC8、CRC12、CCITT CRC16、ANSI CRC16、CRC32。这次我只完成了CRC8的算法,至于CRC16或CRC32下次再研讨。

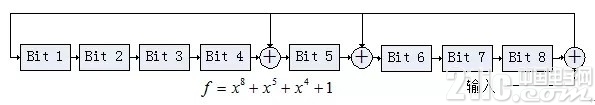

关于CRC的基本原理咱们能够依据详细的硬件电路图来了解,一般CRC循环冗余校验能够表明为带有反应的移位寄存器,移位寄存器的阶数便是CRC字节的位数。另一种表明办法是将CRC表明为 X的多项式,X的幂次数便是CRC字节相应的位数,系数为“1”表明相对应阶数的寄存器有反应,系数为“0”表明无反应。

核算之前先将移位寄存器悉数清零,然后将数据一位一位地串行方法输入移位寄存器,当所要核算的有用数据最终一位输入后,此刻移位寄存器中的值便是所输入这段有用数据的CRC8校验值。

咱们能够经过CRC8的两个重要性质来验证咱们事前CRC8算法的正确性,这两个性质在接下来的仿真进程中要用到:

1)当CRC8的移位寄存器的初始值为八位的数据A时,假如将相同的8位数据A顺次输入给移位寄存器,寄存器将清零。也能够说成是A除以A余数为0。

2)当CRC8的移位寄存器的初始值为八位的数据 时,假如咱们将 的反码 顺次输入给移位寄存器,移位寄存器的成果将是35H,也便是十进制的53。使用该特性能够对CRC8算法进行验证。

算法完成

以上所介绍的这种串行移位寄存器的方法主要是协助咱们把握CRC校验的基本原理,当然完成上也能够用Verilog言语完成这种硬件电路,可想而知这种方法核算起来是适当慢的,要1个clk核算1bit。常用的CRC8算法是查找表算法。

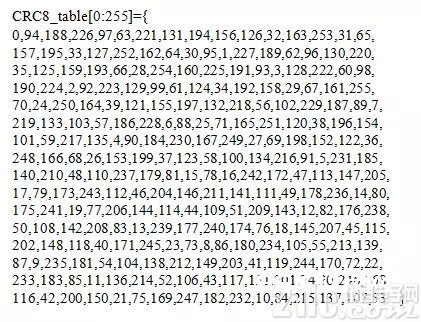

该算法是以一次输入8位数据din为单位的,也便是说一个时钟内并行输入一个字节数据,下一个时钟即可算出CRC8校验字节。使用Verilog言语先界说一个CRC8字节的寄存器,在CRC8寄存器内容的基础上,使用新输入的8位数据核算新的CRC8字节来更新CRC8寄存器。假如CRC8寄存器初始值为0,那么输入8位数据后核算得到的CRC8就有256种或许。因而,界说了一个查找表reg [7:0] CRC8_table[255:0]并初始化为如下所示:

下面说下完成该算法的进程:输入的8位数据din即作为查找表CRC8_table的索引i = din,然后履行CRC8 《= CRC8_table句子就得到了该字节的CRC8校验码,但是以上进程的条件是CRC8寄存器初始化为0,若CRC8寄存器不为0,那么查找表的索引i 的核算应为当时CRC8与输入数据的异或,即 i = CRC8^din,然后履行句子CRC8 《= CRC8_table就得到了新的CRC8校验码。顺次循环处理每个字节。。。。。。

首要界说了个module

SCLK输入时钟,在上升沿对输入数据din[7:0]收集,使能信号EN, 核算成果CRC8[7:0]

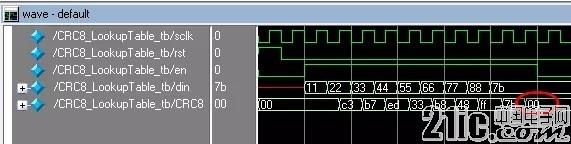

仿真成果:

1)输入数据顺次为:8‘h11 8‘h22 8‘h33 8‘h44 8‘h55 8‘h66 8‘h77 8‘h88 在最终一个字节的下一个时钟上升沿得到校验成果为8’h7b

2)依据性质一,假如咱们持续输入8‘h7b,得到的成果将是8’h00

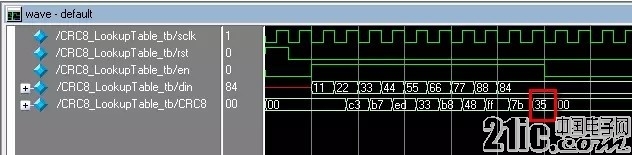

3)依据性质二,8‘h7b的反码是8’h84,假如在1)数据的基础上持续输入8’h84,将得到8‘h35,在封装IP核的进程中咱们只需要上一步的.v文件,也便是CRC8_LookupTable.v文件。

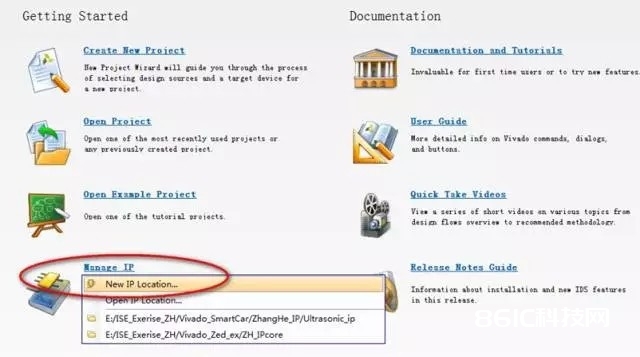

1)翻开vivado, 点击 manage IP 创立新IP,如下图:

2)挑选IP核工程途径:CRC8_LUT_IP这个文件夹是之前创立的,今后咱们一切的创立的文件都在这个文件下,这个途径很重要

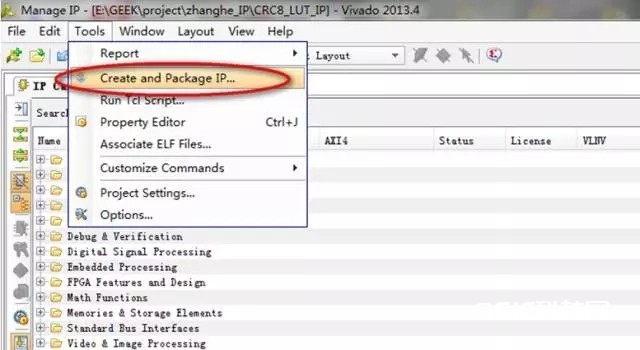

3)点击finish后,在TOOL下拉菜单挑选Create and Package IP

4)点击next,挑选Create New AXI4 Peripheral,留意默许的途径是 CRC8_LUT_IP/managed_ip_project ,这个事过错的,假如在这个途径下的话,在接下来的进程中会遇到过错,将途径改为: CRC8_LUT_IP下