首要小编就几个关键技能再给咱们介绍一下。

差分时钟技能

差分时钟是DDR的一个重要且必要的规划,但咱们对CK#(CKN)的效果知道很少,很多人理解为第二个触发时钟,其实它的实在效果是起到触发时钟校准的效果。

因为数据是在CK的上下沿触发,形成传输周期缩短了一半,因而必需求确保传输周期的安稳以确保数据的正确传输,这就要求CK的上下沿距离要有准确的操控。但因为温度、电阻功用的改动等原因,CK上下沿距离或许产生变化,此刻与其反相的CK#(CKN)就起到纠正的效果(CK上升快下降慢,CK#则是上升慢下降快),如下图一所示。

图一 差分时钟示意图

数据选取脉冲(DQS)

就像时钟信号相同,DQS也是DDR中的重要功用,它的功用首要用来在一个时钟周期内准确的区别出每个传输周期,并便于接纳方准确接纳数据。每一颗8bit DRAM芯片都有一个DQS信号线,它是双向的,在写入时它用来传送由主控芯片发来的DQS信号,读取时,则由DRAM芯片生成DQS向主控发送。彻底能够说,它便是数据的同步信号。

在读取时,DQS与数据信号一起生成(也是在CK与CK#的交叉点)。而DDR内存中的CL也便是从CAS宣布到DQS生成的距离,数据真实呈现在数据I/O总线上相关于DQS触发的时刻距离被称为tAC。实践上,DQS生成时,芯片内部的预取现已结束了,因为预取的原因,实践的数据传出或许会提早于DQS产生(数据提早于DQS传出)。因为是并行传输,DDR内存对tAC也有必定的要求,关于DDR266,tAC的答应规模是±0.75ns,关于DDR333,则是±0.7ns,其间CL里包含了一段DQS的导入期。

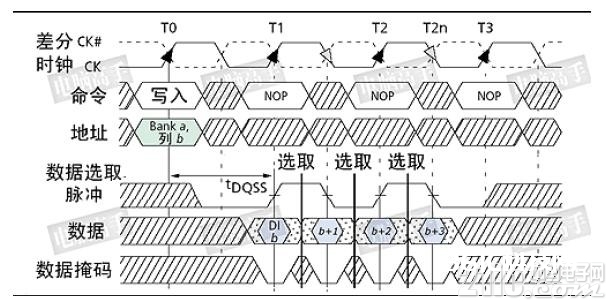

DQS 在读取时与数据同步传输,那么接纳时也是以DQS的上下沿为准吗?不,假如以DQS的上下沿区别数据周期的风险很大。因为芯片有预取的操作,所以输出时的同步很难操控,只能约束在必定的时刻规模内,数据在各I/O端口的呈现时刻或许有快有慢,会与DQS有必定的距离,这也便是为什么要有一个tAC规则的原因。而在接纳方,全部有必要确保同步接纳,不能有tAC之类的误差。这样在写入时,DRAM芯片不再自己生成DQS,而以发送方传来的DQS为基准,并相应拖延必定的时刻,在DQS的中部为数据周期的选取切割点(在读取时切割点便是上下沿),从这儿分离隔两个传输周期。这样做的长处是,因为各数据信号都会有一个逻辑电平坚持周期,即便发送时不同步,在DQS上下沿时都处于坚持周期中,此刻数据接纳触发的准确性无疑是最高的,如下图二所示。

图二 数据时序

数据掩码技能(DQM)

不是DDR所特有的,但关于DDR来说也是比较重要的技能,所以一起介绍下。

为了屏蔽不需求的数据,人们采用了数据掩码(Data I/O Mask,简称DQM)技能。经过DQM,内存能够操控I/O端口撤销哪些输出或输入的数据。这儿需求着重的是,在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。

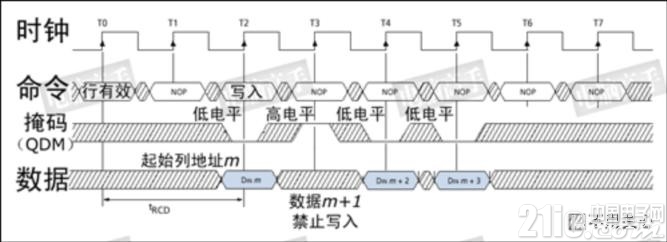

DQM由主控芯片操控,为了准确屏蔽一个P-Bank位宽中的每个字节,每个64bit位宽的数据中有8个DQM信号线,每个信号针对一个字节。这样,关于4bit位宽芯片,两个芯片共用一个DQM 信号线,关于8bit位宽芯片,一个芯片占用一个DQM信号,而关于16bit位宽芯片,则需求两个DQM引脚。SDRAM 官方规则,在读取时DQM宣布两个时钟周期后收效,而在写入时,DQM与写入指令相同是当即收效,如下图三和四别离显现读取和写入时突发周期的第二笔数据被撤销。

图三 读取时数据掩码操作

图四 写入时数据掩码操作

所以DQM信号的效果便是关于突发写入,假如其间有不想存入的数据,就能够运用DQM信号进行屏蔽。DQM信号和数据信号一起宣布,接纳方在DQS的上升与下降沿来判别DQM的状况,假如DQM为高电平,那么之前从DQS中部选取的数据就被屏蔽了。

有人或许会觉得,DQM是输入信号,意味着DRAM芯片不能宣布DQM信号给主控芯片作为屏蔽读取数据的参阅。其实,该读哪个数据也是由主控芯片决议的,所以DRAM芯片也无需参加主控芯片的作业,哪个数据是有用的就留给主控芯片自己去挑选。

好了,前面介绍了DQS的功用,那么咱们在测验时依据DQS和DQ的波形是怎么区别数据的读写操作的?

在DDRx里边常常会被一些缩写误扰,如OCD、OCT和ODT,我想有相同困扰的大有人在,现在笔者来介绍一下咱们的这些困扰吧。

片外驱动调校OCD(Off-Chip Driver)

OCD是在DDR-II开端参加的新功用,并且这个功用是可选的,有的材料上面又名离线驱动调整。OCD的首要效果在于调整I/O接口端的电压,来补偿上拉与下拉电阻值,然后调整DQS与DQ之间的同步确保信号的完好与可靠性。调校期间,别离测验DQS高电平和DQ高电平,以及DQS低电平和DQ高电平的同步状况。假如不满足要求,则经过设定突发长度的地址线来传送上拉/下拉电阻等级(加一档或减一档),直到测验合格才退出OCD操作,经过OCD操作来削减DQ、DQS的歪斜然后进步信号的完好性及操控电压来进步信号质量。详细调校如下图五所示。

图五 OCD

不过,因为在一般状况下对使用环境安稳程度要求并不太高,只需存在差分DQS时就根本能够确保同步的准确性,并且OCD 的调整对其他操作也有必定影响,因而OCD功用在一般台式机上并没有什么效果,其长处首要表现在对数据完好性十分灵敏的服务器等高端产品范畴。