为给DSP、ASIC、FPGA和微处理器的负载点供电而引起的电压输入轨数目的增多使得电源规划愈加具有挑战性。特别是由于体系功率和作业频率要求的增加,形成基础设施、工业和工厂自动化设备对噪声和其他不行猜测事情愈加活络。例如,体系发动时的过错输入电压会引起体系闩锁、牢靠性问题乃至体系故障。

本文评论怎么针对FPGA或微处理器装备各种电压输出盯梢和时序操控选项,来协助完成活络多电源轨体系的正确发动和关断。咱们还将剖析比率和同步盯梢设置,用于避免FPGA的内置静电放电二极管 (ESD) 在上升和下降输出期间偏压或过度受压。这些装备可明显进步体系牢靠性,这对确保广泛的基础设施体系和工厂车间工业设备的生产率和正常运转时刻非常重要。

体系装备

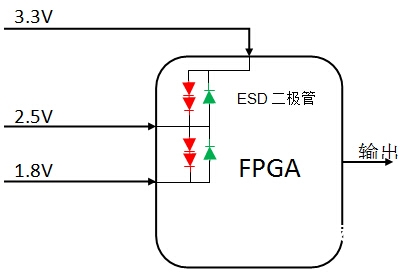

图1显现了针对FPGA的典型运用电路装备。从3.3V最高输入轨到2.5V第二输入轨,咱们发现一组背对背ESD二极管装备充任内部维护电路。另一组背对背ESD二极管装备是从第二输入轨至第三输入轨。

图1. FPGA输入框图

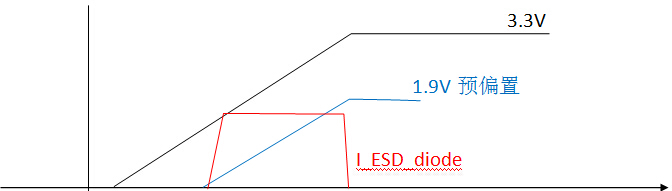

咱们假定一种最高输入轨(在这个比如中为3.3V)最早发动的状况。然后,其将2.5V输越轨预偏置至约1.9V,将1.8V轨预偏置至1.2V。相似地,假如1.8V轨首要发动,则其对2.5V和3.3V轨进行预偏压。在任一种状况下,ESD二极管都必须在发动期间导电。图2显现了3.3V输入轨的电压信号及其在发动前发送至2.5V轨的信号。流经ESD二极管的充电电流取决于发动压摆率、2.5V输出电容以及任何负载。以1.8V输越轨履行相同的发动情形会显现相似的电压信号。

图2. 3.3V和2.5V预偏置的发动波形

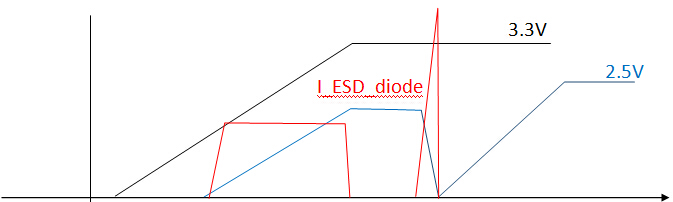

每逢ESD二极管导电时,其牢靠性就会下降。图3显现了当2.5V输入源未设定为带有预偏置发动功用时3.3V和2.5V轨会产生什么状况。能够看到,FPGA的内置ESD二极管在2.5V轨发动时遭到压力。因而,运用带有预偏置发动功用的电源可避免该问题和避免体系或许呈现的闩锁。正确的装备降压稳压器的输出电压盯梢功用可确保一切体系电源轨一同正确软发动,并避免ESD二极管导电。这个简略过程可进步体系牢靠性和避免任何意外的体系电源闩锁。

图3. 3.3V和2.5V的发动波形

集成式FET DC/DC转换器

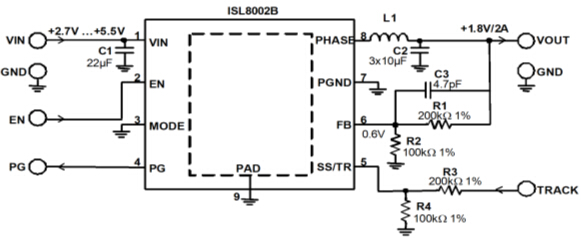

图4显现了输入电压规模为2.7V – 5.5V的2A DC/DC转换器的典型运用电路。只运用了几个外围元件,包含需求的电阻、电容和电感。转换器集成了补偿电路和功率MOSFET来确保规划牢靠性、最小元件数目和可达95%的高效率。

图4. ISL8002B的典型运用原理图

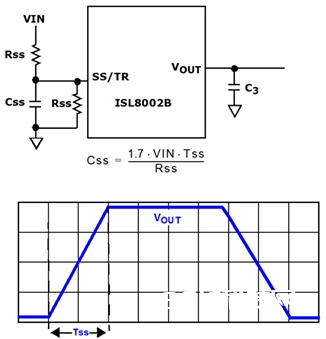

转换器的引脚5一同供给软发动 (SS) 和输出盯梢 (TR) 功用。当该引脚衔接高电平时,软发动时刻在内部设置为1ms。可是,运用外围元件可完成各种软发动计划。图5显现了怎么运用SS/TR功用来编程外部软发动时刻。

图5. 外部软发动装备

经过设置软发动电阻RSS和%&&&&&%CSS可调整软发动时刻。相应的近似联系如式1所示:

式1

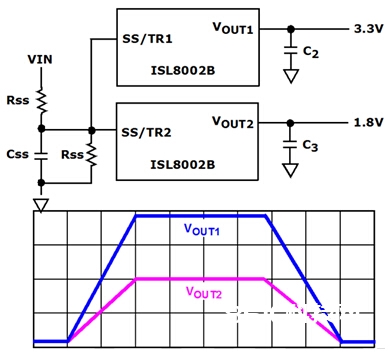

别的还可装备该软发动功用来盯梢其他输出。图6显现了Vout1-Vout2的比率盯梢装备。

图6. Vout1-Vout2的比率盯梢

此外,还能够经过将两个SS/TR衔接到一同来使两个输出电压一同上升。相似地,关断功用还可彼此进行比率盯梢,好像式1中描绘的软发动时刻相同。

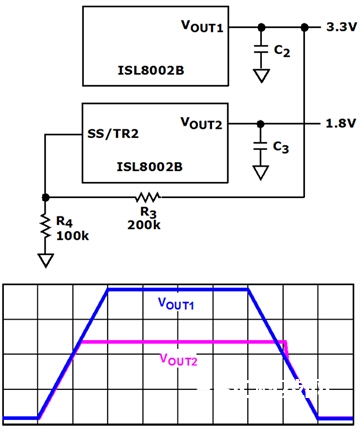

同步盯梢装备如图7所示。只需增加一个电阻分压器,其比率与其在反应回路中的输出电压感测分压器的比率相同。在此状况下,一切输出电压依照主轨以相同的电压和斜率上升。一般,一切其他输越轨应当盯梢最高电压轨。然后,每个输出将在到达其稳定点后分支。经过很好地操控一切输越轨的发动和关断,可避免图1的内置ESD二极管导电或正向偏置。最重要的是,该规划技能可避免体系牢靠性下降、闩锁以及更坏的状况:体系故障。

图7. Vout1 – Vout2的同步盯梢

结束语

比如ISL8002B等集成FET式步降稳压器,为加电和断电期间的电压盯梢供给了很多易于运用的解决计划。任何体系电压盯梢需求简直都能够运用本文评论的电路进行装备。这些装备不限于两个稳压器,由于它们能用于体系中的任何数量的电压轨。只需求将一切SS/TR引脚衔接到一同即可进行比率盯梢。别的还可运用电阻分压器来对体系进行同步盯梢编程。无论是比率盯梢仍是同步盯梢办法均可避免ESD二极管接受不必要的压力,然后进步体系的全体牢靠性。

作者简介

Tu Bui是Intersil公司的工业与基础设施产品运用工程司理。他担任开关稳压器产品研制及一切相关客户运用支撑作业。在参加Intersil之前,Bui先生是ATT贝尔实验室的Technical Staff Design Engineer成员,在那里他研制和推出了超越20种世界级产品及产品族。Bui先生具有亚利桑那大学的电气工程学士学位 (BSEE) 和南边卫理公会大学的工程办理硕士学位。