1引 言

跟着SOC(体系芯片)规划使命复杂度的进步,功用验证已成为体系规划中最大的瓶颈。关于百万门级的SOC芯片,每次投片的NRE是巨大的,估计,在未来两年,验证在规划中所占的比重将到达50%以上。因为SOC体系遍及触及实时环境下的使用,现有的仿真东西不或许处理一切的功用验证问题,有必要使用FPGA在挨近实时的条件下进行软硬件协同验证。根据多片FPGA完成的验证往往面对体系切割的应战。盲意图、短少优化的体系切割,不只很或许在归纳、切割、板上完成呈现屡次重复,糟蹋许多的时刻,并且也难以确保FPGA验证成果与ASIC规划的共同性。

本文在传统鸿沟区分的基础上,通过静态时序剖析东西,使用要害途径时延信息,对切割进程进行束缚。新的验证战略注重体系切割在时序收敛、面积、数量和管脚数等方面的平衡,意图是使切割成果趋于合理,验证环境愈加挨近SOC规划原型,防止传统FPGA验证在体系切割、归纳和规划等环节的重复迭代,完成了验证和SOC开发调试的同步。文章一起评论了该办法关于信号完好性剖析的奉献。

终究,通过一个切割实例,就切割功率与传统办法进行了比照。

2传统的FPGA验证流程

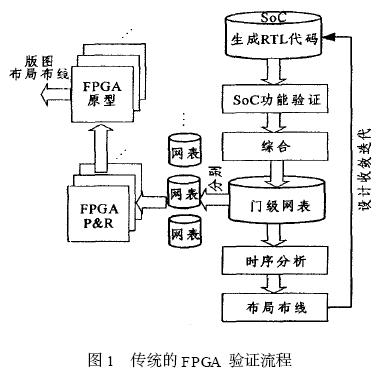

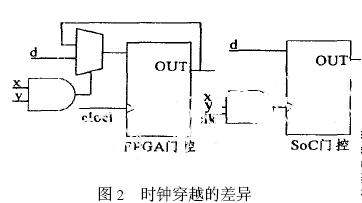

传统的FPGA验证流程如图1所示。这种归纳与切割彼此无关的验证流程存在许多缺点。首要,从ASIC结构到FPGA结构的转化存在差异,例如,许多SOC体系规划经常会处理时钟信号穿越“与”、“或”、“与非”等门的状况,如图2所示。

此刻,归纳东西一般不会主动选用FPGA专有的时钟结构,其成果是产生时钟倾斜(clockskew),导致ASIC代码和归纳出来的FPGA在功用上不共同。即,假如疏忽时钟树在时钟域规模的分散效应,切割时很有或许导致从ASIC结构到FPGA结构的转化的不共同。这个比方一起阐明,相似的问题相同会在其它电路网络中产生,RTL规划在满意时序收敛要求的开发进程中,不管选用的是动态验证仍是静态验证技能,都应当注重电路网络中途径推迟的影响。传统FPGA验证的体系分区切割战略一般选用沿天然鸿沟区分的方法,规划者片面上一般过火依托几许拓扑联系和层次化的体系模块区分,特别是疏忽了切割进程与归纳和时序剖析的联系。这种过于简单化的切割战略很或许会导致不合理的成果,FPGA验证所映射的或许是没有意义的ASIC结构。

3 根据要害途径时延束缚的FPGA验证流程

3.1要害途径时延提取

关于FPGA验证,咱们以为,高功率的体系切割至少应该具有两个条件:找到最佳的切割点和在体系级上迫临规划。首要,切割在技能上是可行的,答应将规划区分为多个适于单个FPGA完成的模块,在挨近实时的环境下进行验证。现在最大的FP2GA规范封装可供给400到440个I#710;O,对I#710;O的管脚数意图支撑不再成为切割的瓶颈,这也为传统的沿着内核或模块的鸿沟进行直接区分供给了空间。在确认最佳切割点的重复迭代进程中,咱们发现,使用静态时序剖析取得的要害途径时延信息,彻底能够用于完成收敛性更好的体系切割。静态时序剖析是一种检查ASIC规划逻辑和时序的东西,其主要意图是核算各通路的功用,辨认牢靠的踪影,确诊树立和坚持时刻的合作。静态时序剖析会剖析陈述一切要害途径,包含一些重要的调试信息,比方每个网络节点的扇出或容性负载等。

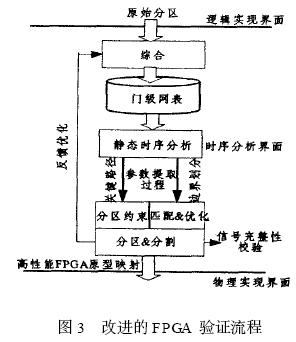

通过实践发现,使用要害途径时延信息对体系切割和归纳进行束缚,能够确保切割依照相对确认的规范进行,取得时序优化的成果,然后有用地削减了功用验证进程中的重复。一起,为使验证进程更为挨近AS%&&&&&%功用,切割时尽量做到面积、晶体管数量和管脚的匹配,确保切割的成果对面积和I#710;O使用而言都是合理的毛病定位要求。这些办法均优化了FPGA验证进程,所取得的归纳分区和时序收敛成果更好,为终究物理地图验证铺平了路途。咱们选用的具体办法是,首要根据静态时序剖析陈述确认要害途径的分区门限,然后原则上沿着功用鸿沟将推迟长的途径切割到同一个FPGA分区,通过更进一步的归纳分区,取得收敛性更好的途径。其成果是,能够将需求验证的勘探点更多地切割到FPGA鸿沟,到达进步I#710;O使用率的意图。显着,高的I#710;O使用率能够有用地拓展FPGA验证规模。通过改进的FPGA验证流程如图3所示。

该流程的优势在于:切割是依照确认的规范进行的,针对传统验证流程的时序剖析,仅仅对布局布线有用的缺点,环绕时序剖析这个中心,将逻辑完成和物理完成有机地结合在一起,侧重考虑了要害途径时延对FPGA切割功率的影响,使切割成果更为合理。此外,新流程通过在归纳、时序仿真进程、切割验证中交互进行静态时序剖析,完成了归纳、切割、验证、规划的高效同步。在要害的时延信息和鸿沟条件束缚下,通过迭代,功用块延时和布线延时,能够取得与实践比较共同的作用,多片FPGA完成时的代码修改量也得到削减。Xilinx、Altera等FPGA出产商大多支撑兼容的第三方时序剖析东西,使用时选用Synopsys的PrimeTime进行静态时序剖析。该东西的优势在于不要求用户输入鼓励或测验矢量,可通过调用db格局的网表文件,便利地检查要害途径或指定通路的时序。

3.2 信号完好性的确保

新流程对SOC验证功率的另一奉献,是供给了一种在代码级优化信号完好性的途径,有利于在归纳和板级验证的进程中对信号完好性施行动态的操控,及早发现规划中躲藏的严峻的信号完好性缺点。信号完好性(SignalIntegrity,SI)是指传输线上的信号质量及信号守时的精确性。SOC芯片规划一般要求数据必须在时钟触发沿树立之前安稳,才干确保逻辑操控的精确性。应当注意到,摩尔定律所躲藏的另一层意义是,RTL体系规划要随时敷衍工艺完成条件的改变,因为规划不或许总是针对最新的工艺条件完成的。

新的工艺条件或许会给原规划带来影响。例如,规划从0125Lm工艺转向0118Lm工艺完成时,就存在信号完好性问题。跟着体系速度和处理带宽的添加,信号完好性的影响会表现得愈加杰出。另一方面,传统的RTL规划在规划和验证环节存在与信号完好性剖析脱节的现象,难以发现并批改信号完好性缺点,或许在向更高规范工艺迁移时,因为代码修改量太大,必然加剧体系验证等环节的担负,然后使规划功率大打折扣。因而,咱们的起点是,争夺以最小的代码修改量,完成RTL代码与FPGA的直接映射,确保FPGA功用验证的要求;一起,将信号完好性的影响在验证进程中以更直观的方法表现出来。

剖析标明,最直观的信号完好性问题一般与电路模块之间的互连点有关,这在静态时序剖析中实践上有所反映。特别需求指出的是,新的FPGA验证流程是树立在通过优化的体系切割基础上的。正如上一节所指出,推迟长的途径根本束缚在同一个FPGA分区。通过这样的优化处理,实践上,一方面是对信号完好性有必定的优化;另一方面,因为I#710;O使用率的进步,更多的毛病勘探点切割到了FPGA的鸿沟,信号完好性在协同验证中会得到更多的反映,通过软件全速仿真,比较简单查找和定位规划缺点,及早消除规划危险;一起,为RTL代码的动态优化供给了根据,有利于在规划前期尽量削减信号完好性缺点,使之习惯工艺条件改变的才能更强,进步规划的稳健性。通过采纳以上办法,咱们在原SOC规划的基础上,以较小的代码修改量,完成了从0125Lm向0118LmCMOS工艺的滑润过渡,并通过了体系后仿真。

4 体系切割验证成果

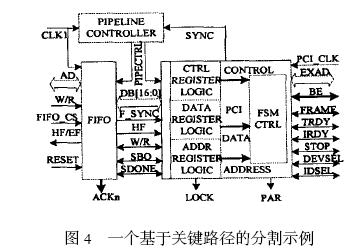

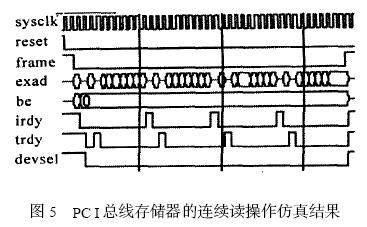

FPGA切割选用XilinxISE根据网表的集成验证环境,选用三种XC4000系列器材(XC4003、XC4005、XC4010)生成验证原型。该系列器材能生答应规模内的恣意频率,可便利地提取片上和片外的精确50#710;50占空比的时钟,时钟边际的守时精度到达1%。加之通过改进的时钟布线,验证环境比较挨近高功用SOC的实践要求,能够确保验证环境与SOC体系坚持最大极限的共同。图4是选用地址#710;数据复用完成的PCI接口模块的FPGA切割成果。其间,PCI操控单元选用两级操控流水方法完成与FIFO的高速数据交换,流水线操控信号彻底束缚在FPGA鸿沟内部。图5是FPGA在布局布线后,50MHz体系时钟下PCI接口64字节数据缓冲存储器读操作的后仿真成果。

这种更为精确的切割验证相同会给板级测验带来便利。硬件仿真时,能够使用逻辑剖析仪的数据接口测验流到勘探头的信号,也能够通过串口或以太网接口对逻辑剖析信道进行收集剖析,快捷地测验FPGA之间的传递信号。通过改进的FPGA切割验证战略比较精确地反映了信号网中的路由拓扑,包含FPGA内部组合逻辑推迟、信号通过FPGA鸿沟所需的时刻;毛病的定位也相对简单,某些毛病还能够提早预知。在进一步的验证工作中,使用了6片XC4000对一个根据Verilog言语完成的的SOC体系(包含VLIW处理器核、总线操控器、I#710;O接口等)进行了切割(规划是以较小粒度的方法完成的,这样切割作用更为理想)。全芯片软件固化鼓励测验的成果与RTL测验成果彻底共同。表1列出了改进计划与传统切割成果的数据比照。成果标明,I#710;O使用率有显着的进步,逻辑操控块的使用率也有所改进,进一步证明了计划的有用性。

5结 论

本文探讨了一种通过优化的SOC体系的FP2GA协同验证战略,依托静态时序剖析东西,使用要害途径时延对切割进程进行束缚,明显改进了传统的沿天然鸿沟切割的功率,验证成果更为挨近SOC运转环境。新的协同验证流程完成了SOC规划与FPGA验证的同步,削减了不必要的重复迭代环节,有利于扫除体系规划阶段或许导致体系失效的要素,加大了体系规划出产调试一次成功的或许性。