USB(Universal Serial Bus,通用串行总线)以其无需装备、即插即用等特性获得了广泛的运用。2004年提出的USB2.0标准,传输速度最大能够到达480Mbps。但在 USB3.0标准中,它的最大传输速度几乎是传统USB2.0传输速度的10倍,到达了5.0Gbps,被界说为“超高速U S B接口”。本文依据CYPRESS的FX3系列USB3.0芯片,对USB3.0总线进行研究开发。

2.USB3.0接口芯片概述

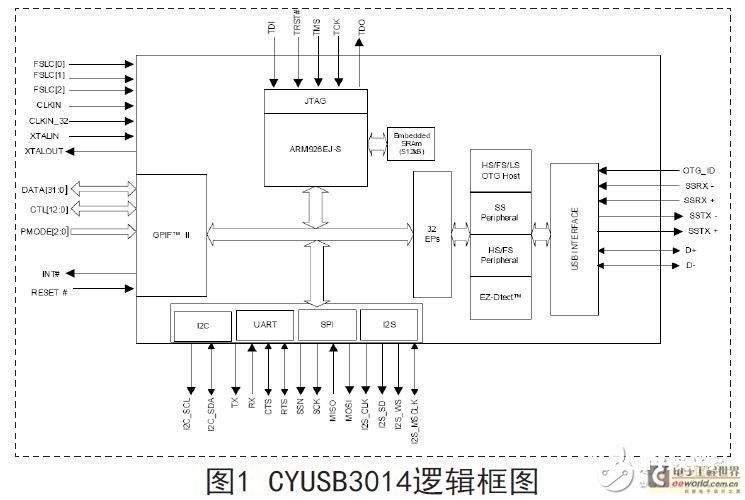

赛普拉斯的EZ-USB FX3是新一代的USB3.0外设操控器,具有高度集成的灵敏特性,答应体系规划者将USB3.0增加至任何体系。本文选用的是FX3系列USB3.0芯片CYUSB3014

FX3是彻底兼容USB3.0 V1.0和USB2.0标准的,集成的USB2.0 OTG操控器答应芯片作为主从设备运用。别的,它还支撑一些常用的外设接口,如SPI,I2C,UART和I2S能够与外部设备进行通讯。

FX3具有一个可进行彻底装备的并行通用可编程接口GPIF II,它能够与任何处理器、AS%&&&&&%或是FPGA衔接。它能够轻松无缝地衔接至多种常用接口,比方异步SRAM、异步和同步地址数据复用式接口、并行 ATA等等。EZ-USB FX3集成了USB3.0和USB2.0物理层(PHY)以及32位ARM926EJ-S微处理器,具有强壮的数据处理才能,并可用于构建定制运用。

3.体系全体规划

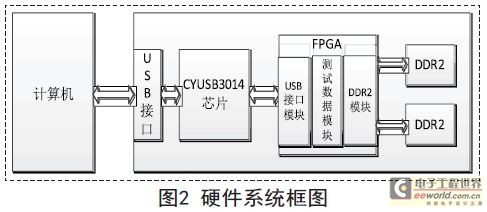

本体系规划首要由软件部分和硬件部分组成。软件部分首要包含三大部分:PC机运用程序、FX3固件程序FPGA程序。硬件部分首要由FPGA、USB3.0芯片和DDR2组成,硬件的体系框图如图2所示。本文首要完成了硬件、PC机运用程序和FPGA程序的规划。

FX3固件程序运用的是Cypress的SDK开发包的固件程序。

3.1 DDR模块规划

与FPGA比较,USB3.0接口是一个高速的接纳单元。在不同作业速度的体系之间,数据缓存是不可或缺的部分,一般来说,运用FIFO根本能够使各体系作业在自己的时钟频率下,而不需求重复的相互握手信号就能进行数据的沟通。本文规划的数据是保存在核算机上,因为各核算机的硬件装备可能会不一样, 咱们规划了DDR2虚拟FIFO模块来进行数据缓存,为批量传输时能够供给满意的缓存,不必忧虑为缓存不行电脑来不及存取数据形成数据丢掉。

本体系选用两片MT47H64M16HR,两片DDR并联操控总线和地址总线,总存储容量到达2Gbit,读写宽度都为16bit,它具有丰厚的资源,满意满意本体系的需求。

3.2 USB3.0接口规划

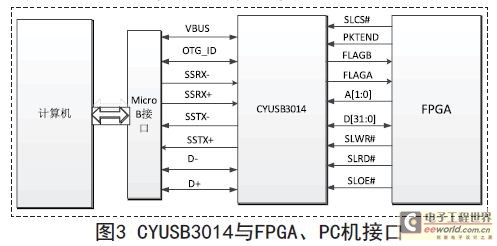

与USB2.0不同的是,USB3.0在与核算机通讯时,它有自己专用的数据通路,专用的数据发送线路和独立的数据接纳线路,即图3中四线差分信号 SSRX+/-和SSTX+/-,然后能够真实的完成全双工。一起,USB3.0还兼容了USB2.0的D+/-信号接口,然后能够与USB2.0无缝衔接。运用从器材FIFO接口与FPGA链接,传输速度能到达可到达320MBps。图3为USB芯片与FPGA和PC机的电路衔接。

3.3 FPGA逻辑规划

FPGA是整个体系的中心,它需求发生测试数据并将数据存储到DDR2中,以及将DDR2中读出的数据转移到CYUSB3014大的内部FIFO中,因而它首要由如图2内部所示模块构成。

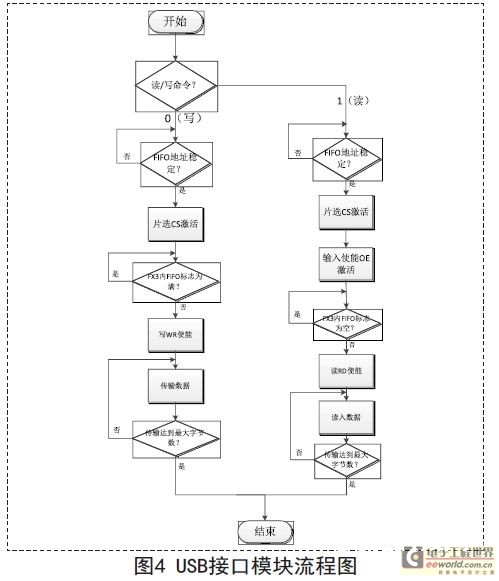

3.3.1 USB接口模块

USB接口模块首要处理读写指令。读写指令需求核算机经过USB操控传输,传递到CYUSB3014中,再由CYUSB3014将详细的指令转化为电平信号送到FPGA的IO口。USB接口模块依据UART_RX上的电平信号,判别出是读指令仍是写指令,终究发生CYUSB3014的片选CS、使能 OE、读/写操控等有用信号。