电信职业要求具有很高的服务可用性-正如你一拿起电话就期望听到拨号音相同。跟着宽带服务供给商争相进入音频和视频范畴(随同所谓的”三重播映”的打开),用户期望他们能够在这些范畴完成相同的高可用性。

高可用性只能经过为构成体系的硬件供给冗余性来完成。但是,为了有用办理这种冗余,体系有必要能够监控自己的运转状况,假如产生毛病,体系有必要在 用户觉察到任何毛病停机之前切换到备用硬件。对物理环境的亲近监控,让运营商能够在产生任何部件毛病时采纳积极行动。这触及到监控机架内部的物理环境,利 用各种传感器来记载相关变量,比方温度、电源电压、湿度和冷却功用等。

FPGA是高可用性基础设施中的重要构建模块。因而,应该亲近监控体系内FPGA的片上环境及其周围环境。Xilinx Virtex-5体系监控器能够愈加轻松地监控FPGA及其外部环境。

Virtex-5体系监控器

Virtex-5体系监控器能够让用户轻松取得FPGA片上(晶片)温度和电源条件方面的信息。它还能够经过外部模仿输入通道获取外部传感器信 息(最多能够监控17个外部传感器)。获取上述信息需求很少的规划尽力,乃至不需求,详细取决于所需的功用。常见的功用,比方报警、主动通道定序器和数据 均匀,都能够从体系监控器模块中得到,这样规划人员就能够垂手可得地开宣布一个解决计划。

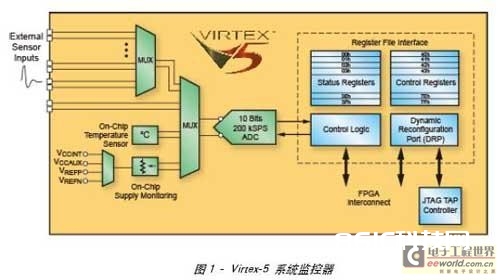

图1给出了Virtex-5体系监控器的结构图。该监控器的中心是一个10位(每秒200,000个采样)模数转换器(ADC)。ADC的模仿输入规模是0~1V。在10比特的分辨率下,该ADC能够处理的输入电压精度大约为1mV。

如图1所示,片上传感器和外部模仿输入通道都经过模仿多路复用器与ADC输入端相连。因而,从不同传感器取得的电压有必要由ADC转化成数字量。 丈量成果被写入状况寄存器,并能够运用FPGA架构或许经过FPGA和PCB的JTAG基础设施从外部轻松读取上述状况寄存器中的数据。运用相同的接口也 能够对监控器的操控寄存器进行读写操作。操控寄存器对体系监控器的操作(例如,针对测验、编程报警极限和传感器均匀的要求挑选适宜的传感器通道)进行配 置。加电后不久体系监控器就彻底进入作业状况,而且在不装备FPGA的条件下就能够进行正确的操作。默许情况下,加电后只会监控片上传感器;但也能够启用 外部模仿输入。装备前只能经过JTAG测验拜访端口(TAP)获取丈量信息。

1. 用户报警

体系监控器的有用内置特性之一是,它能为片上传感器生成报警信号。规划师能够设定上述报警信号的阈值。体系监控器能够自主监控这些传感器,而且只要在检测到报警状况时才会对体系宣布报警。

体系监控器还含有一个工厂设置的报警状况,被称为过热报警(OT)。一旦启用该功用,假如检测到晶片温度高于125℃,体系监控器就会恳求封闭 整个芯片。当晶片冷却到设定的温度水平常,才给晶片加电。在芯片掉电期间,体系监控器会持续操作片上传感器,而且对其进行监控。

默许情况下不会启用OT功用,假如需求,有必要清晰启用此功用方可收效。

2. 对“查验器”进行查验

为了让Virtex-5体系监控器供给准确而又牢靠的环境信息,需求对丈量数据和体系监控器操作进行牢靠性查看。体系监控器具有很多有助于保证 操作牢靠性的功用。ADC的内置主动校准功用和传感器能够纠正模仿丈量体系中由作业环境形成的任何漂移。自检功用还能让体系主机对体系监控器的运转状况进 行监控。

运用体系监控器JTAG拜访功用

Virtex-5体系监控器还具有一个新功用,即经过JTAG TAP拜访模块的一切功用。经过完成模仿测验和拜访模仿信息,您能够运用体系中现有的JTAG取得更大的价值和功率。在装备FPGA(该FPGA作为实践 生产中PCB测验计划的一部分)之前或正常操作的过程中,能够拜访这些功用,然后简化了调试。

为了简化PCB的电源电压和电流之类的片外丈量,您能够在装备FPGA之前运用特别的JTAG指令来为外部模仿输入创造条件。即便装备完 FPGA,体系监控器也不需求在规划中进行清晰例示,因而能够经过JTAG TAP拜访那些用于完成调试功用的特性,即便是在规划后期。为了保证体系监控器的可用性,仅有的要求在于,有必要供给正确的PCB支撑。这触及与体系监控器 用户指南中描绘的外部2.5V参阅IC进行衔接的问题。

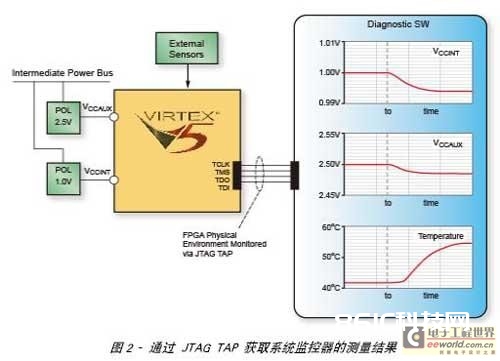

图2显现了一个典型确诊使用,在正常操作时对FPGA的物理运转环境进行监控。在图2的比如中,体系监控器用于调查大电流需求期间(从t0时间 开端)功率分配体系(PDS)中的电压(IR)降。在上述高活动期间,咱们还监控了FPGA的温度。能够在开发阶段敏捷承认电源或PCB规划的潜在问题。 JTAG拜访功用还供给了一个简洁的办法,能够承认特定规划是否配有恰当的冷却体系。ChipScope Pro分析器能够轻松拜访体系监控器;而且,这种拜访功用还能够轻松地集成到其它JTAG测验和编程环境中。

体系集成

除了能够运用JTAG TAP轻松拜访体系监控器之外,还能够经过FPGA架构拜访体系监控器的操控和状况寄存器。运用FPGA架构能够在任何时间对这些寄存器进行装备和读取。 答应经过JTAG TAP操控器和架构接口对体系监控器的寄存器进行两层拜访,并供给了相应的裁定计划来办理或许呈现的争用现象。

在规划中例示体系监控器,并在FPGA装备过程中对其初始化时,还能够界说这些寄存器的内容。因而,能够对体系监控器进行装备使其以用户自界说 的运转(后装备)方式发动。架构接口便是咱们所熟知的动态重装备端口(DRP)。DRP是一个并行的16位同步数据端口(类似于block RAM)。

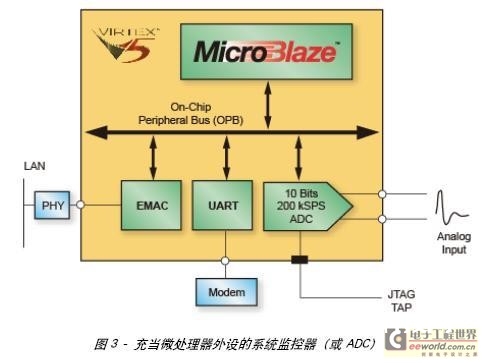

关于需求对体系监控器进行更多操控的高档使用(此刻)而言,DRP能够让体系监控器轻松地映射到硬/软微处理器的外设地址空间中。图3显现了一 个典型体系办理使用,这儿M%&&&&&%roBlaze处理器运转一个类似于协议的智能渠道办理接口(IPMI),而且经过办理通道(如以太网,乃至是简略的 UART/调制解调器)与体系主机进行通讯。

体系监控器还以通用ADC的方式供给了一个重要的微处理器外设。这是业界初次将微操控器中常见的模仿外设集成到FPGA中。此外,该体系还能够彻底操控ADC操作。ADC供给了很多采样方式,而且支撑单极、双极和全差分模仿输入计划。

本文小结

Virtex-5体系监控器为一般的片上和外部环境监控需求供给了一个大大简化了的解决计划。其功用拜访需求很少的开发和规划作业。经过将体系 监控器和JTAG TAP操控器衔接在一起,JTAG功用现已延伸到新的使用范畴,然后完成了新的测验才能。咱们十分期望收到您对本文所说到的任何专题的定见和反应信息,特 别是咱们的开发部队怎么更好地为您的体系监控和测验需求供给支撑。