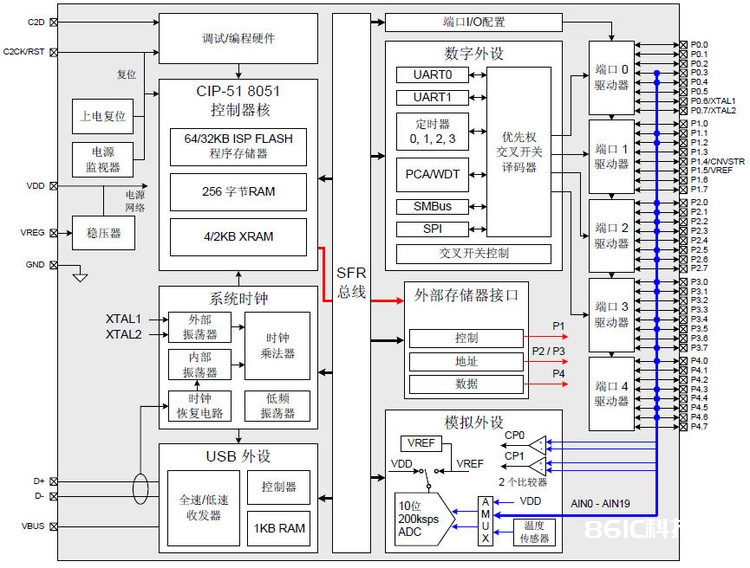

运用Silicon Lab的专利CIP-51微操控器内核,能够运用规范803x/805x的汇编器和编译器进行软件开发,CIP-51选用流水线结构,与规范的8051结构比较指令履行速度有很大的进步,70%的指令的履行时间为1或2个体系时钟周期,只要4条指令的履行时间大于4个体系时钟周期。

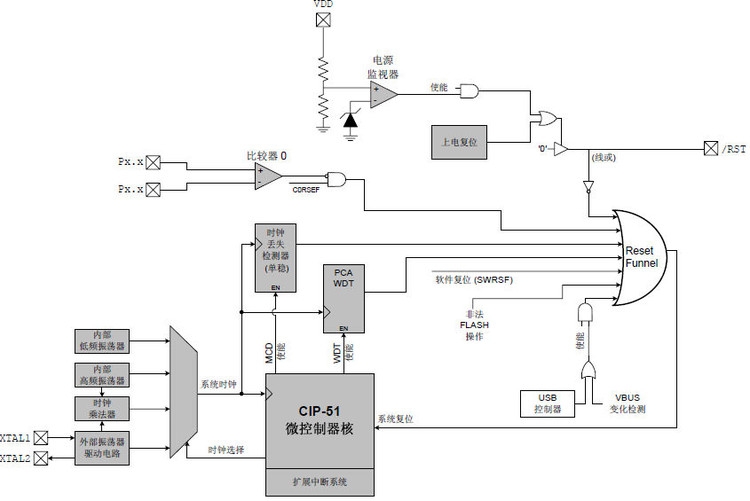

CIP-51共有111条指令。下表列出了指令条数与履行时所需的体系时钟周期数的联系。

器材内部包括一个稳压器(REG0)。当被使能时,REG0输出连到VDD引脚,并可为外部器材供给电源。REG0能够被软件使能/制止。

可在工业温度规模(-45℃到+85℃)内用2.7V-5.25V的电压作业。电源电压大于3.6V时,有必要运用内部稳压器。

包括C2调试接口,支撑FLASH编程和运用安装在终究运用体系中的器材进行在体系调试。

1.根本特性

时钟源:有1个可编程内部高频振动器、1个可编程内部低频振动器、1个外部振动器驱动电路和1个4倍时钟乘法器。

高速内部振动器在出厂时现已被校准为12MHz±1.5%。时钟恢复电路答应内部振动器与4倍时钟乘法器合作,供给全速办法USB时钟源。内部振动器还被用作低速办法下的USB时钟源。器材内集成了外部振动器驱动电路,答应运用晶体、陶瓷谐振器、

电容、RC或外部CMOS时钟源产生体系时钟。

体系时钟能够被装备为运用内部振动器、外部振动器或时钟乘法器输出二分频。假如需求,能够在CPU运转时切换体系时钟振动源。低频内部振动器或外部振动器在低功耗体系中对错常有用的,它答应MCU从一个低频率(节电)的时钟源运转,当需求时再周期性地切换到高速时钟源。

运用外部振动器时,有必要在OSCXCN寄存器中挑选外部振动器类型,有必要对一切端口引脚进行装备,关于晶体/陶瓷谐振器、电容或RC办法,应将一切端口装备为模仿输入,关于CMOS时钟办法,应将一切端口引脚装备为数字输入;关于外部晶体或陶瓷谐振器,有必要在XTAL1和XTAL2引脚之间并接一个10MΩ的电阻。运用RC、%&&&&&%或CMOS时钟装备,时钟源应接到XTAL2引脚。

外部晶体运用进程:a.使能外部振动器;b.等候至少1ms;c.查询XTLVLD =>‘1’;d.将体系时钟切换到外部振动器。

4倍时钟乘法器装备:a.经过向寄存器CLKMUL写0x00来复位时钟乘法器;b.用MULSEL位挑选时钟乘法器的输入;c.用MULEN位使能时钟乘法器(CLKMUL | = 0x80);d.延时大于5 μs;e.用MULINIT位初始化时钟乘法器(CLKMUL | = 0xC0);f.查询等候MULRDY =>‘1’。

当运用外部振动器作为4倍时钟乘法器的输入时,外部振动源有必要在乘法器初始化之前被使能并安稳运转。

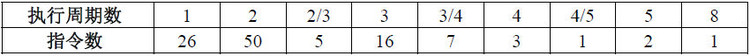

有9个复位源:上电复位电路(POR)、片内VDD监视器(当电源电压低于VRST时强制复位)、USB操控器(USB总线复位或VBUS状况改动)、看门狗定时器、时钟丢掉检测器、由比较器0供给的电压检测器、软件强制复位、外部复位输入引脚和FLASH读/写过错维护电路复位。除了POR、复位输入引脚及FLASH操作过错这三个复位源之外,其他复位源都能够被软件制止。在一次上电复位之后的MCU初始化期间,WDT能够被永久性使能。

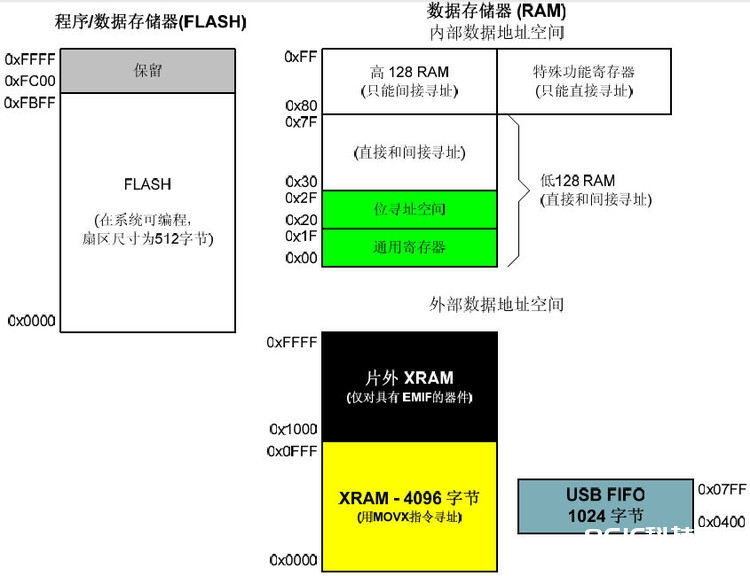

2.存储器

1)程序存储器

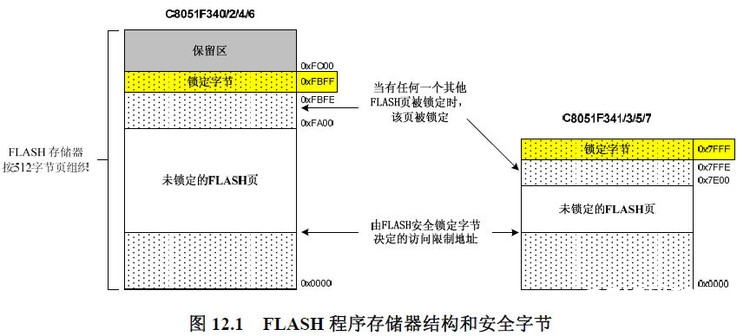

内部有可再编程的FLASH存储器,用于程序代码和非易失性数据存储。能够经过C2接口或由软件运用MOVX指令对FLASH存储器进行在体系编程,每次一个字节。可在体系编程,扇区巨细为512字节。

64KB的片内FLASH存储器可用作程序存储器或可编程数据存储器,实际运用进程中需注意,程序默许从低地址开端寄存,如需运用该空间寄存数据,需避开程序代码区。只要未确定的FLASH页可运用。

2)数据存储器

片上256字节RAM+4KB的XRAM,1KB的USB FIFO也能够被映射到外部数据存储器空间,作为通用数据存储器运用。有用于拜访片外存储器和存储器映射器材的外部存储器接口EMIF。

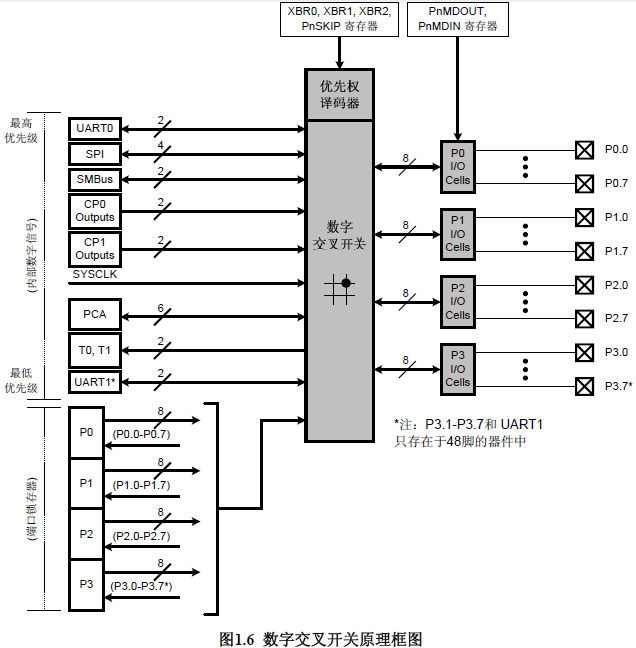

3.通用I/O口

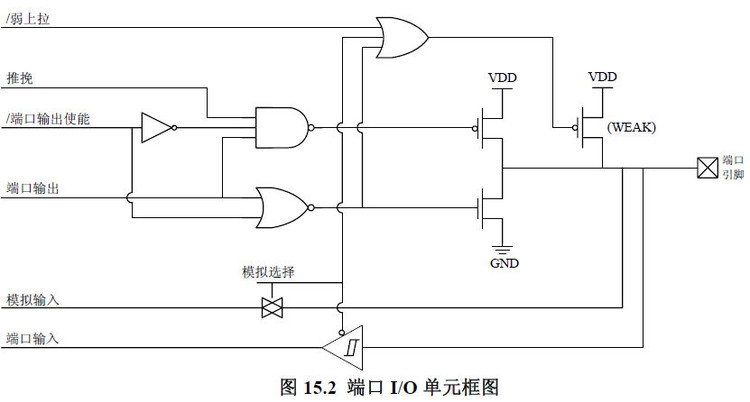

有40/25个I/O口,均耐5V电压,大灌电流。每个端口引脚都能够被装备为模仿输入或数字I/O引脚,被挑选为数字I/O的引脚还能够被装备为推挽或漏极开路输出。

数字交叉开关答应将内部数字体系资源映射到端口I/O引脚,交叉开关依据优先权译码表为所挑选的内部数字资源分配I/O引脚。寄存器XBR0、XBR1和XBR2用于挑选内部数字功用。。PnSKIP寄存器答应软件越过那些被用作模仿输入、特定功用或GPIO的引脚。

a.用端口输入办法寄存器(PnMDIN)挑选一切端口引脚的输入办法(模仿或数字)。

b.用端口输出办法寄存器(PnMDOUT)挑选一切端口引脚的输出办法(漏极开路或推挽)。

c.用端口越过寄存器(PnSKIP)挑选应被交叉开关越过的那些引脚。

d.将引脚分配给要运用的外设(XBR0、XBR1、XBR2)。

e.使能交叉开关(XBARE = 1)。

一切端口引脚都有必要被装备为模仿或数字输入。被用作比较器或ADC输入的任何引脚都应被装备为模仿输入。为使端口P0、P1、P2和P3作业在规范端口I/O输出办法,交叉开关有必要被使能。当交叉开关被制止时,端口输出驱动器被制止。端口4总是作为规范GPIO运用。

未被交叉开关分配的端口引脚和未被模仿外设运用的端口引脚都能够作为通用I/O。经过对应的端口数据寄存器拜访端口P3-0,这些寄存器既能够按位寻址也能够按字节寻址。端口P4(仅C8051F340/1/4/5)运用的SFR只能按字节寻址。

4.中止体系

支撑16个中止源,每个中止源有两个优先级。中止源在片内外设与外部输入引脚之间的分配随器材的不同而改动。

两个外部中止源/INT0和/INT1可被装备为低电平有用或高电平有用,边缘触发或电平触发。IT01CF寄存器中的IN0PL(/INT0极性)和IN1PL(/INT1极性)位用于挑选高电平有用仍是低电平有用;TCON中的IT0和IT1用于挑选电平或边缘触发。

在FLASH写/擦除操作期间和USB FIFO MOVX拜访期间,CPU暂停履行指令。关于在CPU暂停履行指令期间产生的中止,中止服务呼应时间将延伸。

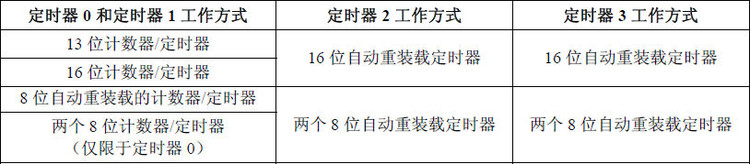

5.定时器

内部有4个16位计数器/定时器:其间两个与规范8051中的计数器/定时器兼容,别的两个是16位主动重装载定时器,可用于ADC、SMBus、USB(帧丈量)、低频振动器(周期丈量)或作为通用定时器运用。这些定时器能够用于丈量时间距离,对外部事情计数或产生周期性的中止请求。

定时器0和定时器1有5个可挑选的时钟源,定时器2和定时器3能够运用体系时钟、体系时钟/12或外部振动器时钟/8作为时钟源。

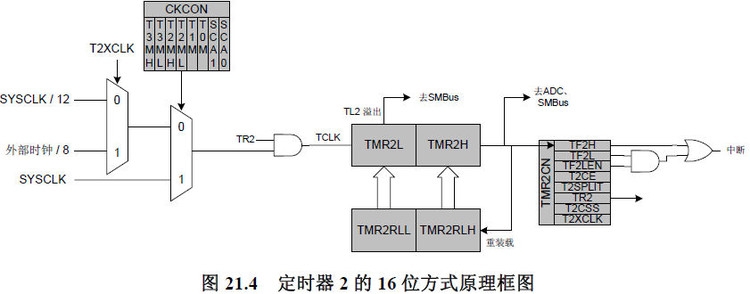

定时器2,3能够作业在16位主动重装载办法、8位主动重装载办法(两个8位定时器)、USB帧开端(SOF)捕捉办法或低频振动器(LFO)下降沿捕捉办法。当T2SPLIT =‘0’且T2SOF =‘0’时,定时器2作业在主动重装载的16位定时器办法:

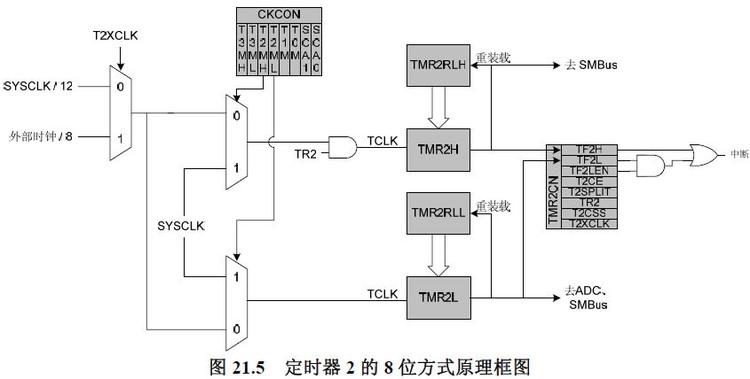

当T2SPLIT =‘1’且T2SOF =‘0’时,定时器2作业双8位定时器办法。两个8位定时器TMR2H和TMR2L都作业在主动重装载办法。TMR2RLL坚持TMR2L的重载值,而TMR2RLH坚持TMR2H的重载值。TMR2CN中的TR2是TMR2H的运转操控位。当定时器2被装备为8位办法时,TMR2L总是处于运转状况。

TF2H和TF2L标志不能被硬件主动铲除,有必要经过软件铲除。

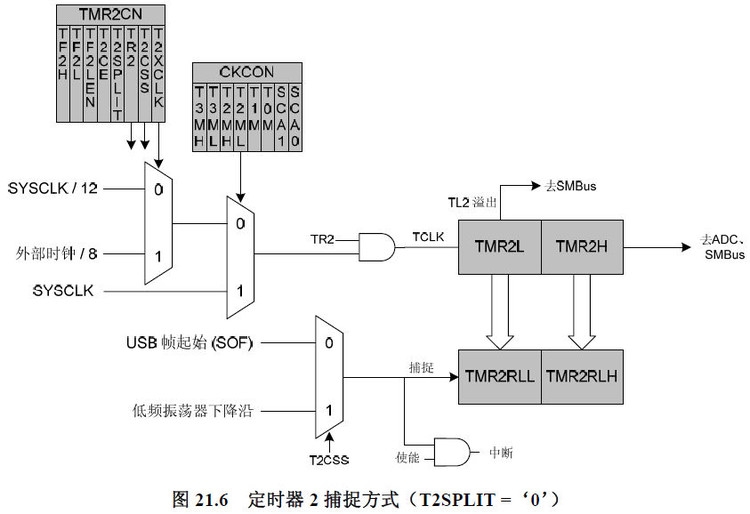

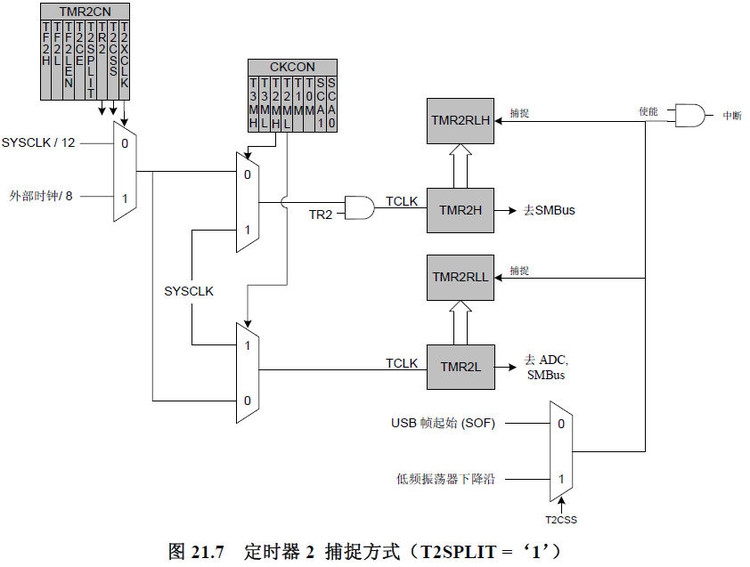

当T2CE =‘1’时,定时器2作业在两种特别捕捉办法之一。捕捉事情能够是USB帧开端(SOF)捕捉或低频振动器(LFO)下降沿捕捉,用T2CSS位挑选。

6.串行口

2个全双工串行口,UART0有2种作业办法:供给规范8051串行口的办法1和办法3。

UART0具有增强的波特率产生器电路,有多个时钟源可用于产生规范波特率,接纳数据缓冲机制答应UART0在软件没有读取前一个数据字节的情况下开端接纳第二个输入数据字节。UART0波特率由定时器1作业在8位主动重装载办法产生。发送(TX)时钟由TL1产生;接纳(RX)时钟由TL1的复制寄存器(RX定时器)产生,TX和RX定时器的溢出信号经过二分频后用于产生TX和RX波特率。定时器1的时钟能够在6个时钟源中挑选:SYSCLK、SYSCLK/4、SYSCLK/12、SYSCLK/48、外部振动器时钟/8和外部输入T1。

UART0的波特率=T1clk/(256-T1H)/2

多机通讯:一切从机的RX和TX别离并接到主机的TX和RX上,从机的MCE0位(SCON.5)被置‘1’,只要当UART接纳到的第九位为逻辑‘1’ (RB80=1)并收到有用的中止位后UART才会产生中止。当主机要发送数据给一个或多个从机时,它先发送一个用于挑选方针的地址字节(地址字节一切从机都接纳,对应地址的从机收到该地址后,清MCE0,以便能接纳数据)。地址字节与数据字节的区别是:地址字节的第9位为逻辑‘1’;数据字节的第9位总是设置为逻辑‘0’。

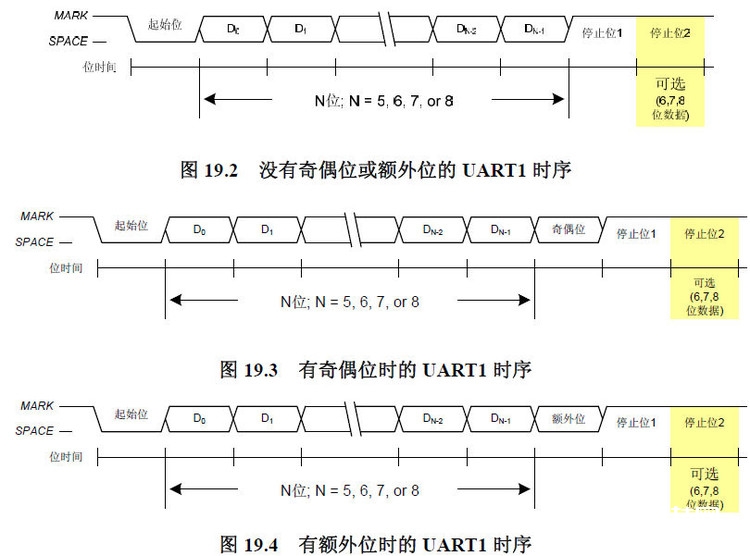

UART1包括一个由16位定时器和可编程预分频器构成的专用波特率产生器,能产生很宽规模的波特率。UART1数据传输以开端位(逻辑低电平)开端,这以后是数据位(LSB在先),数据位之后是奇偶位或额定位(假如挑选),最终是一个或两个中止位(逻辑高电平)。数据长度在5 ~ 8位之间。UART1的作业办法设置与规范51不同。多机通讯时,额定位与UART0的第9位功用相似。

UART1的波特率=Fosc/(65536-(SBRLH1:SBRLL1))/2/预分频值

7.增强型串行外设接口SPI0

增强型串行外设接口(SPI0)供给拜访一个全双工同步串行总线的才能。SPI0能够作为主器材或从器材作业,能够运用3线或4线办法,并可在同一总线上支撑多个主器材和从器材。

8.SMBus

SMBus I/O接口是一个双线的双向串行总线。与I2C串行总线兼容。在作为主或从器材时,数据传输的最大速率可达体系时钟频率的十分之一(这或许比SMBus的规则速度要快,取决于所运用的体系时钟)。能够选用延伸低电平时间的办法和谐同一总线上不同速度的器材。。SMBus供给了SDA(串行数据)操控、SCL(串行时钟)产生和同步、裁定逻辑以及开端/中止的操控和产生电路。

SCL(串行时钟)和SDA(串行数据)线是双向的,有必要经过一个上拉电阻或等效电路将它们连到电源电压。连接在总线上的每个器材的SCL和SDA都有必要是漏极开路或集电极开路的,因而当总线闲暇时,这两条线都被拉到高电平。总线上的最大器材数只受规则的上升和下降时间的约束,上升和下降时间别离不能超过300ns和1000ns。

一切的数据传输都由主器材发动,能够寻址一个或多个方针从器材。主器材产生一个开端条件,然后发送地址和方向位。

一个主器材只能在总线闲暇时发动一次传输。在一个中止条件之后或SCL和SDA坚持高电平现已超过了指定时间,则总线是闲暇的。两个或多个主器材或许在同一时间发动数据传输,所以运用裁定机制迫使一个主器材抛弃总线。企图发送高电平的主器材将检测到SDA上的低电平而退出竞赛。赢得总线的器材持续其数据传输进程,而未赢得总线的器材成为从器材并在后续的传输中接纳数据(假如被寻址)。

每次数据字节或从地址传输都产生SMBus中止。发送数据时在ACK周期后产生中止,使软件能读取接纳到的ACK值;接纳数据时在ACK周期之前产生中止,使软件能确定要宣布的ACK值。

SMBus接口能够被装备为作业在主办法和/或从办法。在任一时间,它将作业鄙人述4种办法之一:主发送器、主接纳器、从发送器或从接纳器。

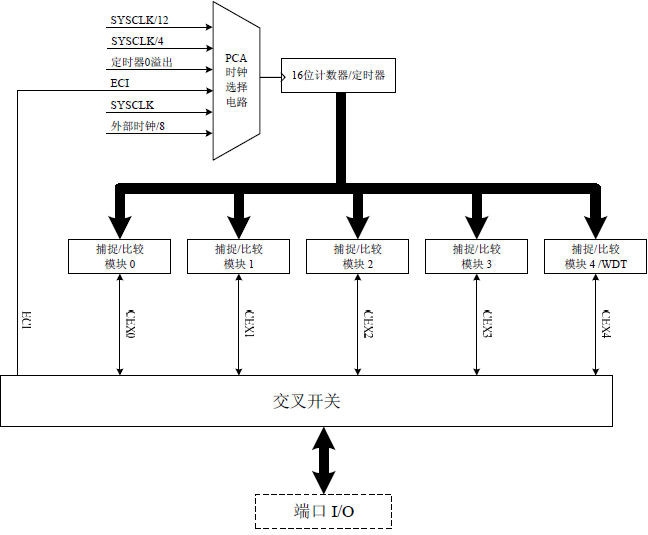

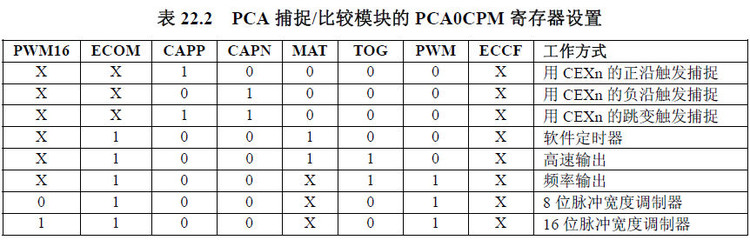

9.可编程计数器阵列(PCA0)

供给增强的定时器功用,与规范8051的计数器/定时器比较,它需求较少的CPU干涉。PCA由一个专用的16位计数器/定时器和5个16位捕捉/比较模块组成。每个捕捉/比较模块有其自己的I/O线(CEXn),这些I/O线在被答应时经过交叉开关连到端口I/O。

定时器的时基信号能够在六个时钟源中挑选:体系时钟、体系时钟/4、体系时钟/12、外部振动器时钟/8、定时器0溢出或ECI输入引脚上的外部时钟信号。

PCA的模块4可被用作看门狗定时器(WDT),在体系复位后即被使能为该办法。在看门狗办法被使能时,对某些寄存器的拜访受到约束

1)PCA计数器/定时器

16位的PCA计数器/定时器由两个8位的SFR组成:PCA0L和PCA0H。在读PCA0L时,“瞬象寄存器”主动锁存PCA0H的值,随后读PCA0H时将拜访这个“瞬象寄存器”;先读PCA0L寄存器能够确保正确读取整个16位PCA计数器的值。

当计数器/定时器溢出时(从0xFFFF到0x0000),PCA0MD中的计数器溢出标志(CF)被置为逻辑‘1’并产生一个中止请求

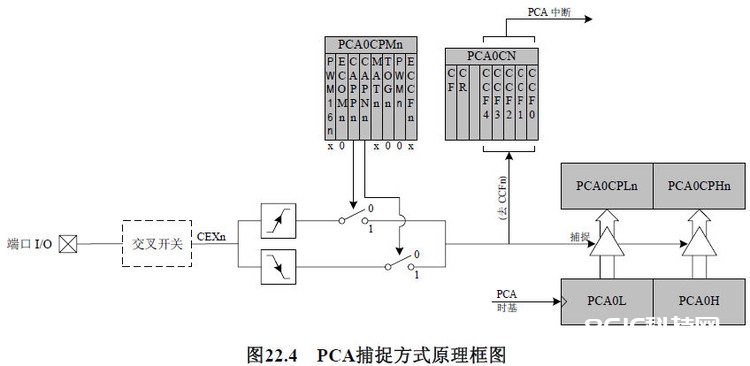

2)捕捉/比较模块

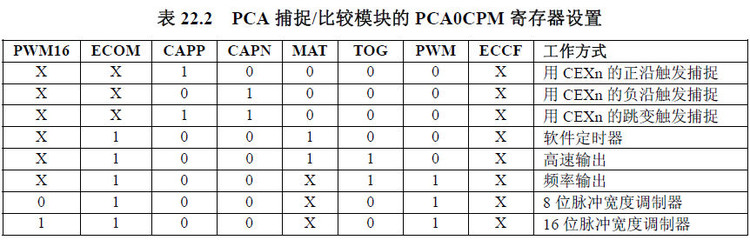

每个模块都可被装备为独立作业,有六种作业办法:边缘触发捕捉、软件定时器、高速输出、频率输出、8位脉宽调制器和16位脉宽调制器。

a.边缘触发的捕捉办法

CEXn输入信号有必要在高电平或低电平期间至少坚持两个体系时钟周期,以确保能够被硬件辨认。

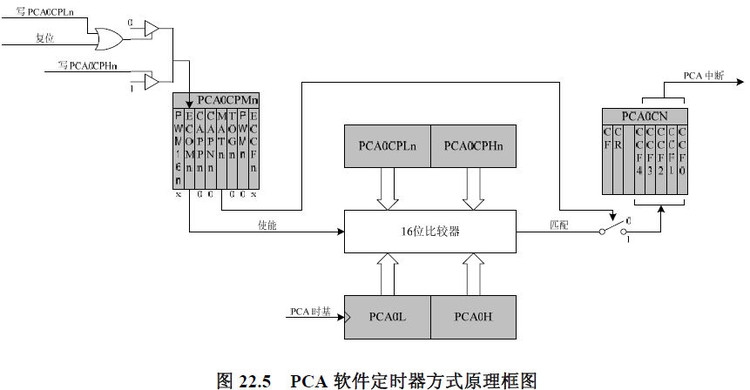

b.软件定时器办法

在该办法,PCA将计数器/定时器的计数值与模块的16位捕捉/比较寄存器(PCA0CPHn和PCA0CPLn)进行比较。当产生匹配时,PCA0CN中的捕捉/比较标志(CCFn)被置为逻辑‘1’并产生一个中止请求;当向PCA0的捕捉/比较寄存器写入一个16位数值时,应先写低字节。

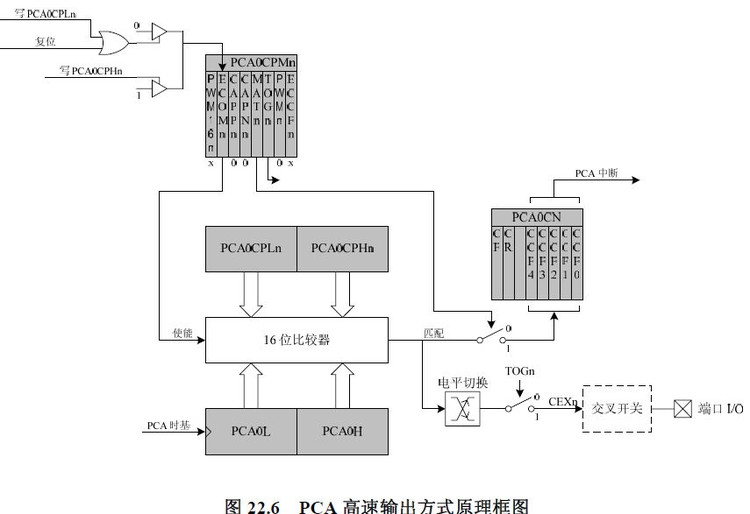

c.高速输出办法

每逢PCA计数器与模块的16位捕捉/比较寄存器(PCA0CPHn和PCA0CPLn)产生匹配时,模块的CEXn引脚上的逻辑电平将产生改动。当向PCA0的捕捉/比较寄存器写入一个16位数值时,应先写低字节。

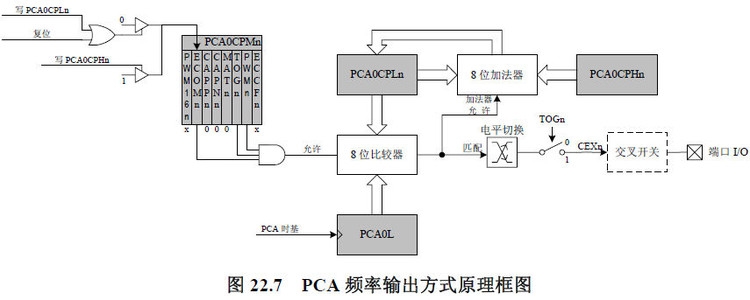

d.频率输出办法

可在模块的CEXn引脚产生可编程频率的方波。。捕捉/比较模块的低字节与PCA0计数器的低字节比较;两者匹配时,CEXn的电平产生改动,

方波频率=Fpca/(2*PCA0CPHn),PCA0CPHn中的值为0x00时,相当于256。

e.8位脉宽调制器办法

PWM输出的频率取决于PCA计数器/定时器的时基。运用模块的捕捉/比较寄存器PCA0CPLn改动PWM输出信号的占空比。当PCA计数器/定时器的低字节(PCA0L)与PCA0CPLn中的值持平时,CEXn引脚上的输出被置‘1’;当PCA0L中的计数值溢出时,CEXn输出被复位

占空比=(256-PCA0CPHn)/256

f.16位脉宽调制器办法

当PCA计数器与模块的值匹配时,CEXn的输出被置为高电平;当计数器溢出时,CEXn输出被置为低电平。为了输出一个占空比可变的波形,新值的写入应与PCA的CCFn匹配中止同步。

占空比=(65536-PCA0CPn)/65536

3)看门狗定时器

经过PCA的模块4能够完成可编程看门狗定时器(WDT)功用。模块4高字节与PCA计数器的高字节比较;模块4低字节坚持履行WDT更新时要运用的偏移值。在体系复位后看门狗被使能。在看门狗被使能时,对某些PCA寄存器的写操作受到约束。

假如在WDT被使能时PCA0CPH4和PCA0H产生匹配,则体系将被复位。为了避免WDT复位,需求经过写PCA0CPH4来更新WDT。在写PCA0CPH4时,PCA0H的值加上PCA0CPL4中保存的偏移值后被装入到PCA0CPH4.

当WDT被使能时:

a.PCA计数器被强制运转。

b.不答应写PCA0L和PCA0H。

c.PCA时钟源挑选位(CPS2-CPS0)被冻住。

d.PCA等候操控位(CIDL)被冻住。

e.模块4被强制进入看门狗定时器办法。

f.对模块4办法寄存器(PCA0CPM4)的写操作被制止。

看门狗定时器偏移值(PCA时钟数)=(256*PCA0CPL4)+(256-PCA0L)

装备WDT的进程如下:

a.经过向WDTE位写‘0’来制止WDT。

b.挑选PCA时钟源(用CPS2-0位)。

c.向PCA0CPL4装入所期望的WDT更新偏移值。

d.装备PCA的闲暇办法位(假如期望在CPU处于闲暇办法时WDT中止作业,则应将CIDL方位‘1’)。

e.经过向WDTE位写‘1’来使能WDT。

f.(选项)经过将WDLCK方位‘1’来确定WDT(避免鄙人一次体系复位前制止WDT)。

WDT在任何一次体系复位之后都被设置为使能状况。PCA0计数器的缺省时钟为体系时钟的十二分频(SYSCLK/12)。当WDTE位被置1时,不能改动PCA0MD寄存器的值。若要改动PCA0MD的内容,有必要先制止看门狗定时器。

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/dianyuan/275618.html