摘要 规划了一种线性F/V转化体系。传感器输出的脉冲频率信号经信号调度电路调度后输入FPGA,FPGA丈量脉冲信号的频率,依据体系精度要求,需规划Q格局定点运算,测得的频率经FPGA定点运算后得到与频率大小成线性联系的D/A转化的数字量,操控串行DAC7551输出相应的电压值。试验成果表明,体系的转化精度优于0.1%,改动体系的规划参数可完成更高精度的频率信号到电压信号的转化。

关键词 F/V转化;精度;FPGA;Q8定点运算;DAC7551

脉冲型流量传感器是流量仪表中一类首要的流量传感器,如涡轮流量传感器、涡街流量传感器、远传型容积式流量计等。这类传感器需将被测参数转化为电模仿量显示出来。频率电压转化器作为一种功用器材,在丈量仪器、自动操控、遥感遥测以及信号传输各个范畴都有着广泛的运用。传统的F/V转化器多选用模仿电路或单片机完成。选用模仿电路规划的F/V转化器多选用如LM331、AD650等完成频率信号到电压信号的转化,规划的体系具有转化精度不高、待测频率规模固定、差错较大的缺陷;单片机规划的F/V转化体系虽然有必定程度的改进,但因为本身测频基准时钟频率的约束,依然无法满意高精度转化的要求。本文依据体系要求:流量传感器输出的脉冲信号频率规模10~3 000 Hz,输出模仿电压信号规模0~5 V,精度优于0.1%。选用FPGA完成脉冲信号频率的丈量,规划的体系满意要求。

1 体系分析

F/V转化的差错首要存在于计数丈量信号周期时的差错、运算时的截位差错和D/A变换器的量化差错等。

首要考虑丈量周期的差错:挑选最大频率信号3 000 Hz,其周期为333.3μs,0.1%差错是333.3 ns。选用12 MHz时钟作为时基信号,周期丈量差错为83.33 ns,对应83.33×5×0.1%/333.33=1.3 mV,差错余量为3.7 mV。

M位D/A转化器的差错为5 000/2(M+1)mV,所以M只需>10位就能够满意精度要求,考虑到D/A本身的差错,能够挑选12位以上且INL1 LSB的D/A,以确保转化精度。

输入的频率信号最小为10 Hz,所以最大计数值为1 200 000,需求21位长的计数器。

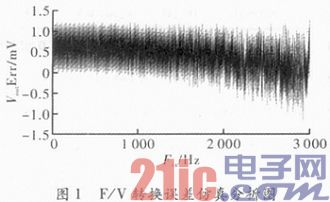

考虑截位差错,运用Matlab仿真,得到运用12 MHz计数频率12位D/A时,需求运用Q8定点运算才干确保体系精度,差错曲线如图1所示。运用Q8格局作定点运算时只需先将数据转化为Q8定点数,然后进行核算,终究将成果转化回一般格局即可(Q格局:小数点坐落第n位元之右侧,称为Qn格局)。

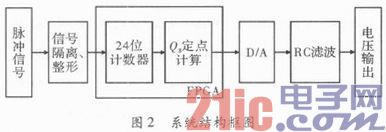

2 体系全体结构

体系全体结构如图2所示。FPGA丈量经阻隔整形后的脉冲信号的频率,经Q8定点运算、截位等处理后得到D/A转化的数字量,D/A输出的电压信号经RC滤波后得到终究与输入脉冲频率大小成线性联系的电压信号。因为流量传感器输出的脉冲信号频率或许会在10~3 000 Hz规模接连改变,不必定是固定值,为确保体系转化精度,使用FPGA计数接连两个待测脉冲上升沿间的时基脉冲个数的办法得到脉冲信号的周期,周期的倒数即为脉冲信号的频率。对固定频率的丈量较为简略,本文首要评论对改变频率的丈量,体系可用于对固定频率的丈量。因为FPGA对待测脉冲信号的处理时刻远小于待测脉冲信号的周期,所以在下一个脉冲到来之前,FPGA现已完成对前一个脉冲的处理。

3 体系电路规划

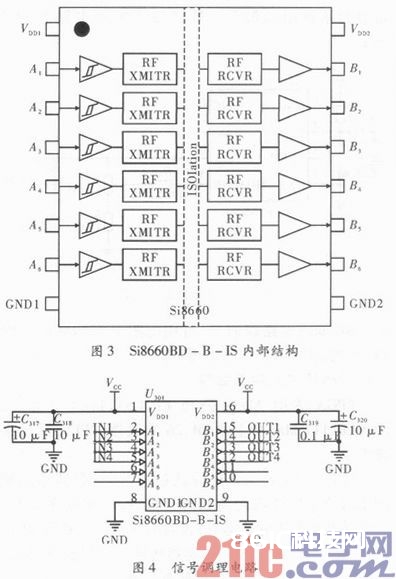

3.1 信号调度电路

为保障体系对信号源的抗干扰才能,传感器输出的脉冲信号需经光电阻隔并整形后再送入FPGA处理。信号调度芯片选用Silicon Labs的低功耗6通道数字阻隔器Si8660BD—B—IS,可完成多路信号一起处理,它具有抗电磁干扰才能强、功耗低、阻隔电压高、寿命长的特色,且具有施密特整形电路的功用。其内部电路如图3所示,信号调度电路如图4所示。

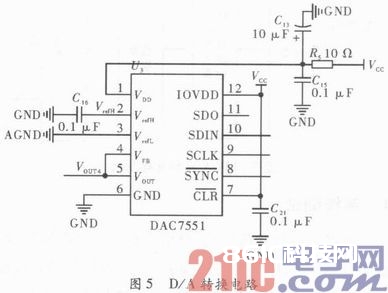

3.2 D/A转化电路

数模转化器是一种数字和模仿混合信号处理电路。D/A转化芯片选用串行DAC7551,+5 V电源供电,12 bit精度,INL为±0.35 LSB,轨至轨电压输出,输出电压树立时刻最大为5μs,输出电阻1Ω,满意体系要求。规划的D/A转化电路如图5所示。

3.3 外部参阅电压电路及RC滤波电路

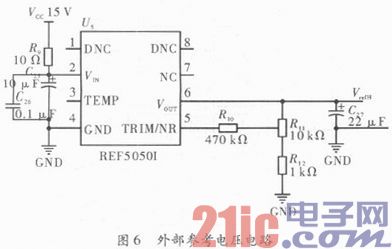

出于对精度及稳定性的要求,期望参阅电压源尽量对供电电源电压和工艺参数以及芯片的作业温度是相对独立的。Ref5050为BB公司出产的高精度+5 V输出稳压模块,最大温度漂移为8×10-6/℃,输出最大差错电压为输出总电压的0.1%,输入电压规模为5.2~18 V,输出电流规模为±10 mA,常作为电路中的基准电压源。外部参阅电压电路如图6所示。

RC滤波电路较简略,可用电阻%&&&&&%构成的一阶RC滤波电路即可,在此不再赘述。

3.4 FPGA内部电路结构

FPGA选用Altera公司EP2C5T144C8 芯片,5000LE、117 kbit片上RAM、26乘法器、2PLL,满意体系需求。

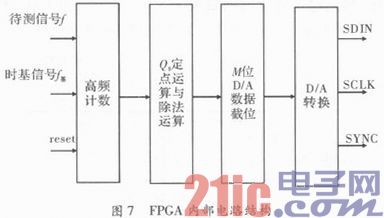

FPGA的首要作业是除法运算,当计数器给出被测信号单个周期内的高频时钟数N,取预存在FPGA中的转化系数做除法运算;再对除法的成果值作M位截位,送外部M位D/A转化器转化,则得到相应的电压值。FPGA内部电路结构如图7所示。

4 体系测验

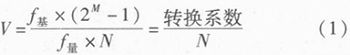

挑选高频时基信号f基对输入信号f的周期计数,得到计数值N,依据线性转化联系,得到F/V的转化如式(1)所示。式中,M是外部D/A转化器的位数,f量是输入脉冲信号的量程即3 000 Hz。

依据式(1)得到的测验成果如表1所示。输入脉冲信号频率规模10~3 000 Hz,D/A芯片选用DAC7551,12 bit精度,选用Q8定点运算确保转化精度。

5 结束语

现在在丈量范畴,脉冲信号既可作为已知的鼓励信号,又可作为不知道的被测信号。作为不知道的被测信号,对其参数测验越显重要。文中规划的F/V转化器选用以FPGA为中心的模块化规划办法,具有测验参数灵敏装备、硬件电路简略、简单完成、测频规模宽、转化精度高级特色。依据体系需求,可灵敏装备体系的参数。添加时基频率、选用精度更高的D/A转化芯片、增大Q运算的阶数都能够完成更高精度的F/V转化。与传统完成办法比较,灵敏性、测频精度、转化精度都得到了大幅提高。