DDR2(Double DataRate2)SDRAM是由JEDEC(电子设备工程联合委员会)拟定的新生代内存技能标准,它与上一代DDR内存技能标准最大的不同:尽管选用 时钟的上升/下降沿一起传输数据的根本方法,但DDR2却具有2倍的DDR预读取才干(即4位预存取技能)。此外,DDR2还添加ODT(内建中心完结电 阻器)功用,内建适宜的端接电阻,避免了以往因片外衔接大片完结电阻带来的制板本钱添加。

依据FPGA的SDRAM操控器,以高可靠性、强 可移植性、易于集成的特色,逐步替代以往的专用操控器而成为干流解决方案。本文选用Xilinx公司的Spartan-3A系列FPGA和Hynix公司 的DDR2 SDRAM器材HY5PS121621完结DDR2操控器的规划。

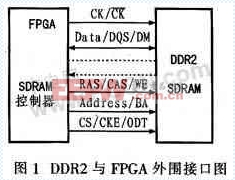

2 FPGA与DDR2存储器接口

图1所示为 DDR2与FPGA的外围接口衔接图,DDR2的信号线分为:时钟信号线CK/CK;数据信号线Data/DQS/DM;地址信号线 Address/BA1/BA0;指令信号线RAS/CAS/WE;操控信号线CS/CKE/ODT。FPGA除与DDR2的一切信号线相连外,还引出外 部环回信号线(图中虚线所示),此信号输出送至输入输出模块(IOB),以补偿FPGA与存储器之间的IOB、器材和迹线的推迟。

差 分时钟线CK/CK为DDR2数据传输供给时钟,在CK的上升沿和下降沿均有数据被触发;双向差分线DQS/DQS看作数据的同步信号,写入时由操控器发 出,读取时由DDR2发生DQS向操控器发送,它与读数据边缘对齐而与写数据中心对齐。DN为数据信号屏蔽位在突发写传输时屏蔽不存储的数 据;RAS/CAS/WE作为指令信号线向DDR2宣布读取、写人、改写或预充电指令;片内完结信号线ODT操控是否需求DDR2进行片内完结。

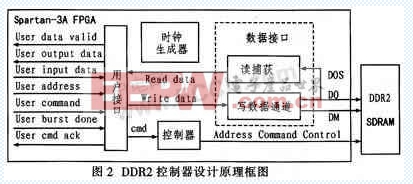

3 DDR2操控器的规划原理

依据FPGA的DDR2操控器规划是由时钟生成模块、存储操控模块和读写数据接口模块组成如图2所示。

控 制器中一切模块时钟均来自于时钟生成模块,它由数字时钟管理器(DCM)操控,输出90°、180°和270°时钟。该模块还包含推迟校准监视器,用于校 准读取数据(DQ)对读取数据选通脉冲(DQS)的推迟,以便读取数据选通脉冲边缘能够正确对齐DQ有用窗口的中心方位。

读写数据接口模 块是整个操控器规划的要害,它担任将用户写入的数据DQ和DOS依照DDR2SDRAM时序要求发送给DDR2,DDR2在DQS的每一个时钟沿收集写数 据。在读取数据时,DDR2SDRAM将DQS和相关数据发送到与DQ对齐边缘的FPGA。FPGA将接收到的DQS信号经过推迟校准,作为内部存储读数 据的FIFO的写时钟。FPGA为DDR2的每个数据位装备一对读写异步的FIFO,每个数据位都输入到上升沿(FIFO0)和下降沿(FIFO1)的 FIFO中,完结原理如图3所示。

存 储操控模块用于发生DDR2所需的地址和指令信号。DDR2在正常的读写操作前要初始化,因而需向DDR2发送初始化指令,待初始化完结后才干发送读写命 令。对DDR2SDRAM的读写访问为突发形式。突发写操作需向DDR2供给写指令(User_command)、写数据 (User_input_data)和写地址(User_address)信号,在最终一个写地址发送突发操作完结信号 (User_burst_done),并坚持2个时钟周期有用下停止写操作,突发写时序如图4所示。突发读操作需向DDR2供给读指令 (User_comm-and)和读地址(User-address),在最终一读地址发送突发完结信号(User-burst_done),并坚持2个 周期有用下停止读操作,突发读时序如图5所示

4 DDR2操控器的规划及使用

为 了缩短开发周期,选用Xilinx的MIG软件东西直接生成DDR2操控器规划模块,包含HDL代码和束缚文件。用户可在MIG的GUI图形界面挑选对应 模板、总线宽度和速度等级,并设置CAS推迟、突发长度、引脚分配等要害参数。假如规划者所选器材与MIG所列模板不相符,可在代码生成后灵敏修正代码, 到达体系要求。代码添加到工程前需硬件验证,选用MIG主动生成的测验模块进行验证。该模块向存储器宣布一系列的写入指令和读取指令,并对写入数据和读回 数据进行比较,经过比较信号(led_error)验证操控器的正确与否。用ChipScope抓取的读数据和相关操控信号时序别离如图6和图7所示,读 写比较信号(led_error)在检测到读写数据持平时输出’0’电平。

在硬件验证经往后,把操控器代码导入到体系工程中,规划者只需输 入相应指令(包含读、写和初始化指令),操控器模块将主动发生指令和操控信号并依照DDR2的时序要求送至DDR2,指令发送结束供给给用户一个指令应对 信号(User_cmd_ack),规划者依据这一信号判别是否能够发送下一个指令。至于主动改写、激活和预充电指令则由操控器主动完结,无需用户干与。

5 结束语

经过MIG东西辅助规划,完结500 M/s带宽的DDR2接口数据收集,占用FPGA资源别离为15%IOB资源,17%逻辑Slice资源和2个DCM。在FPGA中完结DDR2操控器,节约功耗和空间,并缩短体系开发周期,满意大多数低本钱体系规划要求。