题主最近开端触摸和FPGA的计划验证相关的作业内容,需求掌握FPGA内部资源的详细信息,所以又细心查看了官方的器材手册。这一次给咱们共享的内容首要触及Xilinx FPGA内的CLBs,SelecTIO和Clocking资源,合适对FPGA规划有时序要求,却还没有满意了解的朋友。

参阅器材上,尽管一些专用的资源都会集在高端的FPGA类型中,不过题主想了想,仍是把它们放在该系列后续的文章中吧。下文中的举证皆来自Spartan6器材文档,所以也不会超出Spartan6包括内容。

传统的FPGA内部资源分类作三类,可装备逻辑模块(Configurable Logic Block)、输入输出模块(InputOutput Block)和内部布线资源(Interconnect)三个部分,这些咱们都知道的。跟着FPGA的开展,为了满意对信号处理和片上贮存的需求,又在前三类基础上增加了块RAM(BRAM)、时钟办理单元和硬件乘法器,之后又在部分系列里增加了PPC和高速串行输入与输出等等。

下文即将说到的CLB、SelecTIO和Clocking资源里,SelecTIO资源是比较丰厚的一类,所以在次序上把它放在最终。

正文:

首要说说CLB吧,它是一类最重要,其实也是最易于运用的结构。Xilinx把尽可能多的资源装备接口开放给用户,可是出于操控开发周期,而且进步体系安稳性的考虑,CLB不是其中之一,它的装备计划简直悉数由IDE完结进程智能分配,用户能够束缚特别Slice的方位,但很少有这种必要,交给IDE来完结会愈加有用。

来看看它的结构(有一些图片材料不好找,后期整合的时分会补全):

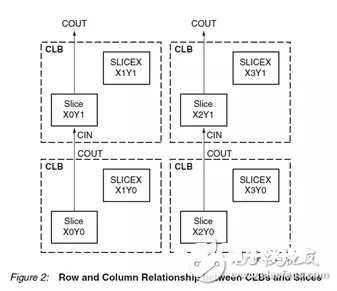

① CLB资源会根据FPGA的尺度被内部时钟网络切割成若干个区域,一般每个区域是40个CLB单元高度;

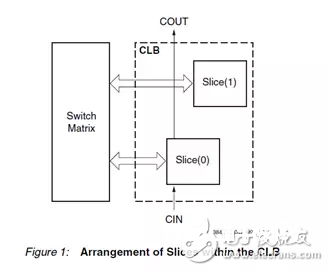

② 每个CLB衔接到一个开关矩阵来接入大局布线矩阵;

③ 一个CLB单元包括 一对Slice单元(两个Slice无直接衔接,而且在CLB间成列散布,每个纵列的Slice有一条独立的进位链);

④ 一个CLB中下方的Slice记为Slice0,上方的记为Slice1;

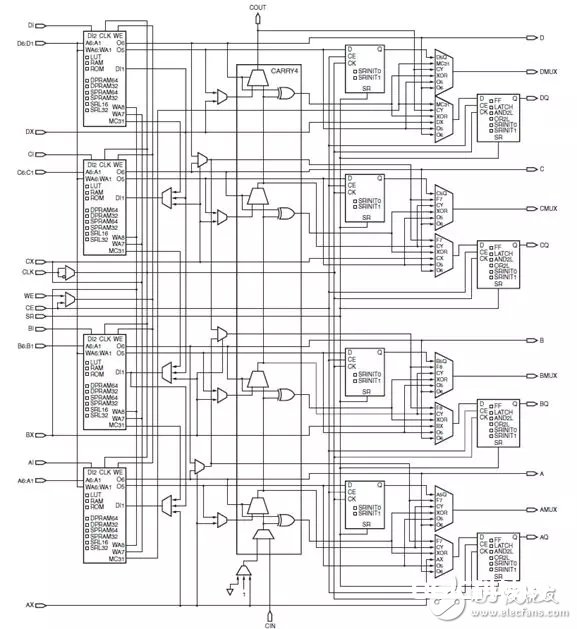

⑤ 每个Slice包括4个查找表(LUTs),8个存储单元(FF),以及一些挑选器和进位逻辑,这些单元用于供给逻辑、算术和ROM功用;

⑥ 有一部分Slice支撑DistributedRAM和32位移位寄存器功用,被记为SLICEM,其他的记为SLICEL(一个CLB最多有一个SLICEM,每个CLB纵列至少有一个SLICEM,在DSP48E(XilinxFPGA内的硬件乘法器)纵列旁的两个CLB纵列,每一个CLB都有SLICEM)。

SLICEM

(DistributedRAM和ShiftRegisters资源都在LUTs上挂载)

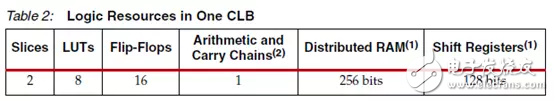

最终看一下一个CLB中的资源总量:

当然详细到Slice中几种资源还有一些细节需求重视,首要是和LUTs的特性相关,不过等后边参加事例来讲吧。假如此前你现已对FPGA规划有一些经历和领会的话,现在想必现已对FPGA的查找表结构有了自己的了解。

仍是简略提及一下LUTs的效果,便是查表,,,在我看来,它便是一个6输入2输出的多功用挑选器,能够直接把Verilog中always块的行为映射到它的行为上,经过对输入端口的衔接装备,它就能够完结咱们需求的信号行为模型。完好的进程今后会参加事例来讲。让咱们缓一口气,先进入下一个内容。

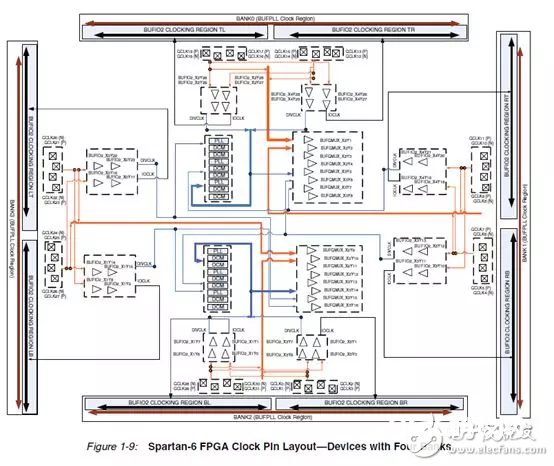

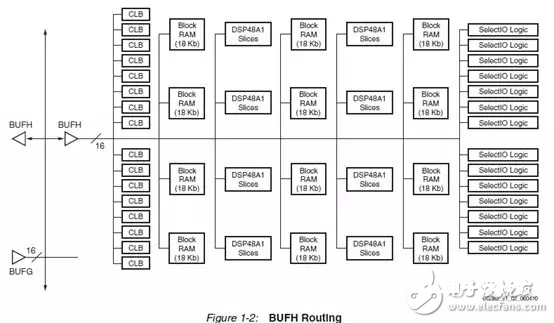

XilinxFPGA内部有杂乱的时钟资源网络,来保护大数量逻辑资源条件下的时序要求和体系安稳。首要分为大局时钟线和部分时钟网络,在Spartan6上,还有数字时钟办理器(DCM)和数字锁相环(PLL)两种硬核资源,用以辅佐时钟资源网络。Spartan6内部供给了16个大局时钟驱动buffer和40个部分时钟的,它们均匀地散布在上文说到的被时钟网络切割出来的各区域中:

咱们能够经过例化BUFG和BUFIO等原语调用这些资源,为GTP(H/X/Z)和DDR、AD/DA这样的高速信号组供给更低相位偏移的时钟参阅,可是时钟资源的分配有比较多的运用规矩,在资源有限而布线窘迫的情况下,经常会被Xilinx规矩查看器奉告运用违例。之后题主会结合一些实在事例来引导咱们去躲避这样的过错。

时钟资源所用的篇幅也很短,事实上触及到时钟的问题许多,可是要在需求的时分再去知道才有价值,否则没有根据的去了解,也没有什么价值。接下来看看FPGA内部最为丰厚的I/O资源,究竟现在市场上FPGA最广泛和最拿手的,便是做接口,下文包括的许多内容,在多个系列的FPGA上都是差不多的规范:

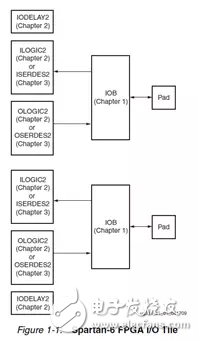

① FPGA的I/O资源被散布在若干个Bank中,每个Bank中有20个I/O TIle;

② 一个Tile包括2个IOB,2个ILOGIC,2个OLOGIC和2个IOEDLAY,用于对双端(差分)信号配对;

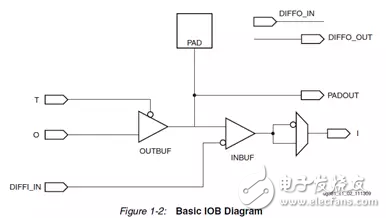

③ IOB包括输入、输出和三态驱动,可装备为不同的I/O规范;IOB直连一对I(O)LOGIC,I(O)LOGIC包括数据I/O的逻辑资源和三态操控,I(O)LOGIC也能够经过调用相关原语装备为I(O)SERDES,完结数据的串并行转化;

IOB单元支撑许多的接口规范,能够对负载才能和转化速率进行操控。而且同Bank内支撑复合电压输出,以驱动一些低压I/O规范,不过对参阅电平的挑选有一些规矩。

关于单端和双端信号I/O,能够挑选许多种buffer装备方法去驱动这些信号,当然IDE的完结进程中也帮咱们装备好了许多,作为用户,常用的像IBUFG、IBUFR这样的时钟驱动资源,IBUFDS、OBUFDS完结信号单双端转化,以及用OBUFT完结三态操控等等。