1、导言

数据收集在工业测控范畴里有广泛的运用,它已成为计算机测控体系的一个重要的环节,尤其在设备毛病监测体系中,因为各种设备的结构杂乱,运动办法多种多样,产生毛病的或许部位很难确认,因而咱们需求从设备的各个部位来提取很多的、接连的数据作为设备状况的信息,以此来剖析、判别设备是否存在毛病,这就需求高速、高功用的数据收集体系来确保收集到的数据的实时性;一起,咱们需求对同一设备的不同方位的信号进行同步收集,并凭借一些手法来提取特征(例如制作轴心轨道图)以判别设备的运转状况。传统的数据收集体系规划中,一般选用单片机或DSP作为主操控器来操控ADC、存储器及其他相关的外围电路来作业。可是这些传统的规划中都存在着一些缺乏,单片机的时钟频率较低且经过软件编程来完结数据收集,难以完结高速、高功用、多通道数据收集体系的要求;DSP尽管速度快,可是它更拿手处理杂乱的数学运算,关于数采体系要求的简略高速的读写操作来说,是一种资源的糟蹋 。而FPGA(现场可编程门阵列)在高速数据收集上具有更大的长处,FPGA体积小、功耗低、时钟频率高、内部延时小、悉数操控逻辑由硬件完结,别的编程装备灵敏、开发周期短、运用硬件描绘言语来编程,可完结程序的并行履行、这将会大大提高体系的功用。

2、体系总体计划

在往复式压缩机状况在线监测体系中,因为压缩机结构杂乱、零部件多、运动办法各不相同,产生的毛病也就会多种多样,因而需求对各个部件的多个测点的模仿信号进行实时数据收集,一起还要对一些测点周围不同的方位的信号进行同步收集,这就对信号收集的同步性有严厉的要求。

多通道的数据收集办法有以下几种:

①各通道模仿信号别离经过信号调度电路后,由多路开关挑选后送入1片高速AD转化器材,多路挑选开关的切换由硬件或软件操控,然后到达别离转化各通道采来的数据。这种计划所需器材少、硬件电路简略、体系结构小型化,但运用多路开关会带来一系列的信号失真问题,且不能完结信号的实在同步收集,这些问题对AD器材和多路开关都提出了较高的要求。

②各通道模仿信号别离经过信号调度电路后,送入各自对应的AD器材,由体系软、硬件操控各AD的同步收集。选用多片无差别AD芯片来完结各通道采样,与常用的模仿多路开关加单片高速AD芯片,确保了信号收集的同步性和实时性,避免了运用多路开关带来的一系列问题如通道切换进程中尖峰电压的处理、开关导通电阻的影响以及高频采样时噪声的按捺等。

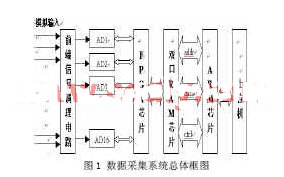

针对往复式压缩机在线监测体系对多路模仿信号收集的实时性和同步性的要求,提出了一种依据FPGA的多通道数据收集的新计划,选用FPGA+ARM相结合的规划,收集主操控逻辑用FPGA来完结,ARM则用来完结收集数据的网络传输操控。本计划中,FPGA向需求同步采样的通道对应的AD芯片供给一致的时钟,使得AD同步地挑选相应的通道进行数据的同步采样和转化,其成果由FPGA同步地接纳并存储在外部双口RAM对应的存储空间,然后由ARM从相应的双口RAM空间读取数据,并经过网络传输给上位机进行处理。其数据收集体系总体规划如图1所示。

该计划将16路信号分为4组,别离对应4块相同的小电路板,每块小电路板选用4片AD,别离由FPGA操控完结4路信号的收集、转化。4块小电路板终究插在一块大的主电路板上,这样可完结体系小型化的要求。体系外形结构如图2所示,图中标号1、2、3、4别离对应四块小的电路板。

3、 体系首要器材的选型

3.1 FPGA芯片的选型及依据

因为本体系收集通道数较多,实时性和同步性要求较高,要求供给的时钟频率高,内部延时小,因而体系挑选Xilinx公司的Spartan3系列XC3S400作为主操控芯片,该芯片具有40万体系门、8064个逻辑单元内嵌18K位块RAM,包括4个时钟办理模块和8个大局时钟网络,最大支撑264个用户I/O。这些丰厚的片上资源在加上其灵敏的编程办法使得该芯片成为最适合的挑选。

3.2 AD芯片的选型及依据

在本计划中,考虑到体系的分辨率、通道数、采样率以及接口等要求,本体系AD芯片选用TI公司的ADS8321[3]。ADS8321是TI公司出产的逐次迫临式串行16位微功耗高速A/D转化器,采样频率最高可达100kHz,具有较小的线性度、较低的噪声和功耗,ADS8321具有同步串行SPI/SSI接口,选用这种串行接口输出数据减小了芯片的体积。

4、 FPGA的逻辑规划

4.1 FPGA的逻辑规划思维

本计划中,体系初始化后,首要上位机将收集的参数信息(采样长度、采样频率、采样办法、通道挑选、增益倍数等等)传送给ARM主操控器,ARM将这些参数信息存入外部的双口RAM中,然后FPGA再依照RAM里的收集参数信息操控履行,完结收集使命,当收集完结后,FPGA将收集到的数据同步地传送到双口RAM对应的存储空间,供ARM来读取,然后ARM在将读到的数据传送给上位机。

4.2 FPGA模块区分

依据以上的规划思维,整个FPGA逻辑模块区分为:时钟逻辑模块、采样操控模块、串并转化模块、通道挑选模块、存储操控模块、接口操控模块。下面详细给出各模块的规划进程。

①时钟逻辑模块。该规划中,外部输入的时钟为50MHz,因为规划中需求多种不同的时钟信号,所以有必要规划一个可依据收集需求恣意分频的时钟逻辑模块,且有必要精确,才干确保整个体系的正常作业。一起该规划选用同步时序电路,它是依据时钟触发沿规划,对时钟的周期、占空比、延时、颤动提出了更高的要求,为此本规划中选用FPGA所带的DCM时钟资源驱动规划的主时钟,已到达最低的时钟颤动和推迟。

②采样操控模块。该模块首要担任操控数据采样和AD转化等,在采样时间到来时,依据ADS8321芯片的作业特性,在CS信号的操控下,芯片便依照时序进行采样、转化,关于ADS8321要注意当16位转化成果输出结束后,置位CS或去掉 DCLOCK脉冲,使成果仅输出一次,否则在Dout端会持续输出转化成果,但此刻是反过因由最低位到最高位顺次输出,直到最高位输出呈现重复时,Dout端变成高阻态。

③串并转化模块。因为ADS8321时以串行输出转化成果的,故需求该模块来将串行输出的数据转化为并行输出,该模块首要选用移位寄存器来完结。

④通道挑选模块。该模块用来挑选需求采样的通道,当ARM主操控器将上位机传来的通道挑选操控字写入双口RAM时,通道挑选模块依据该信息来进行通道的挑选,一起,当数据收集结束后,该模块还为存储操控模块供给相应的地址信号,以便将对应通道收集来的数据存入对应的空间

⑤存储操控模块。双口RAM用于数据缓存,一是存储各AD芯片转化的数据,二是存储ARM主操控器传来的收集参数信息。它具有真实的双端口,能够一起对其进行数据存取,两端口具有独立的操控线、地址线和数据线。该模块便是依据双口RAM读写时序完结对双口RAM的读写操作,已到达缓存数据的意图。

⑥接口操控模块。该模块为ARM向FPGA及其双口RAM进行交互供给桥梁。当ARM向双口RAM写入收集参数信息时,接口模块要将该信息告诉采样操控模块;当ARM读取双口RAM中的数据时,接口模块对ARM的拜访地址进行译码,选中对应的存储空间,取出数据。

4.3软件完结

本规划选用自顶向下的规划办法,选用VHDL来别离规划顶层模块和各底层模块,该言语支撑自顶向下和依据库的规划办法,而且电路仿真和验证机制以确保规划的正确性。下面以采样操控模块为例来阐明其操控算法。

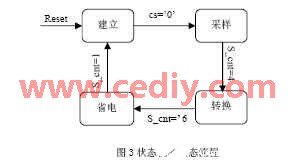

状况机是FPGA内部的指挥单元,它依照固定的节拍往复的运转,本采样操控模块运用状况机来规划,依据ADS8321的作业时序,将状况机分为4个状况周期,别离是树立周期、采样周期、转化周期、省电形式周期,其状况流程如图3所示。

5 、结束语

本文作者立异点是选用FPGA和ARM相结合的规划办法完结高速、多通道、实时的数据收集以及数据的网络传输并选用VHDL编程来完结FPGA各逻辑模块的功用。本规划已经过Modelsim进行的功用仿真和时序仿真,并在Xilinx供给的ISE集成的环境下进行编译、归纳、优化、布局布线,并成功的下载到FPGA芯片中。经过对实践信号的收集、测验,体系作业正常,验证了规划结构的合理性,因而是一种比较抱负的数据收集计划。

责任编辑:gt