导言

自从几十年前初次推出FPGA以来,每种新架构都继续在选用按位(bit-wise)的布线结构。尽管这种办法一直是成功的,可是跟着高速通讯规范的鼓起,总是要求不断增加片上总线位宽,以支撑这些新的数据速率。这种约束的一个结果是,规划人员常常花费很多的开发时刻来测验完结时序收敛,献身功用来为他们的规划布局布线。

传统的FPGA布线根据整个FPGA中水平缓笔直方向上运转的多个独立分段互连线(segment),在水平缓笔直布线的穿插点处带有开关盒(switch box)以完结通路的衔接。经过这些独立段和开关盒能够在FPGA上构建从任何源到任何目的地的通路。FPGA布线的这种一致结构为完结任何逻辑功用供给了极大的灵敏性,可用于FPGA逻辑阵列内的任何数据途径位宽。

尽管在FPGA中的按位来布线十分灵敏,但其缺陷是每个段都会给任何给定的信号通路增加推迟。需求在FPGA中进行长间隔传输的信号会导致分段之间的衔接推迟,然后下降了功用的功用。按位布线的另一个应战是拥塞,它要求信号途径绕过拥塞,这会导致更多的推迟,并形成功用的进一步下降。

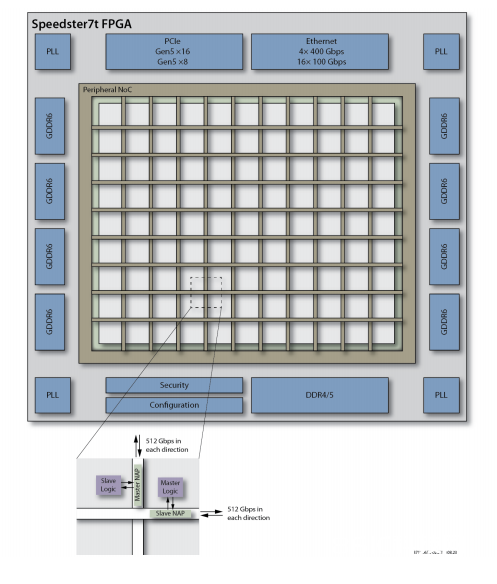

Achronix将此应战视为一个开发全新架构的时机,以消除传统FPGA的规划应战并进步体系功用。Achronix的解决方案是在传统分段式FPGA布线结构之上,再为其全新的Speedster7t FPGA系列器材创立一个革命性的二维(2D)高速片上网络(NoC)。Speedster7t NoC衔接到一切片上高速接口:400G以太网、PCIe Gen5、GDDR6和DDR4 / 5的多个端口。

NoC的内部由一组行和列组成,它们在整个FPGA逻辑阵列中将网络数据流量从水平缓笔直方向上进行分发。主NoC接入(NAP)点和从NoC接入点坐落NoC的每一行和每一列穿插的方位。这些NAP能够是NoC和可编程逻辑阵列之间的源或目的地。

Ethernet:以太网

Security:安全性

Configuration:装备

each direction:每个方向

Speedster7t的NoC好像只对FPGA内部的布线总线有所协助;可是,这种新式架构能够明显进步规划人员的作业功率,完结全新的规划功用,并供给了轻松完结密集型数据处理运用的才能。下面列举了在功率进步、规划变更和功用进步方面最明显的八种运用场景。

图1:Speedster7t的片上网络(NoC)和接口

在整个FPGA的逻辑阵列中简化高速数据分发

在传统的各种FPGA架构中,对衔接到FPGA的片外存储器以及与之相连的外部高速数据源进行双向的读/写操作,需求数据在FPGA逻辑架构中经过一条较长且分段的路由途径。这种约束不只约束了带宽,而且还会耗费在逻辑阵列中的用户规划所需的布线资源,这给FPGA规划人员在时序收敛方面带来了应战,尤其是其他逻辑功用对器材利用率进步的时分。

运用Speedster7t的NoC将数据从外部源传输到FPGA和存储器,比运用传统的FPGA架构完结相同的作业要简略得多。Speedster7t NoC增强了FPGA阵列中传统的可编程互连,其间的NoC就像一个叠加在城市大街体系上的高速公路网络。尽管Speedster7t FPGA中传统的、可编程互连矩阵依然适用于较慢的本地数据流量,但NoC能够处理更具应战性的、高速的数据流。

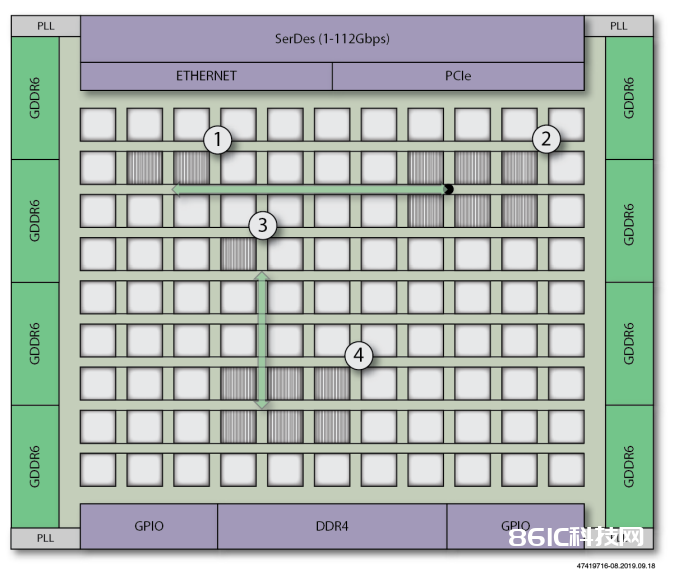

NoC中的每一行或每一列都被完结为两个256位的、以2 Ghz固定时钟速率运转的单向数据通道。行具有东/西通道,列具有北/南通道,然后答应每个NoC行或列能够一起处理每个方向上512 Gbps的数据流量。总而言之,这些通道能够经过编写简略的Verilog或VHDL代码,在FPGA阵列中传输很多的数据,这些代码支撑FPGA与NAP通讯并衔接到NoC高速公路网络上。

下图显现了NoC中各个点之间的数据传输。点1和点2的逻辑别离实例化了一个水平NAP。NAP能够发送和接纳数据,可是每个独自的数据流都只是朝向一个方向。类似地,点3和点4的逻辑实例化了一个笔直NAP,而且能够在彼此之间发送数据流。

图2:NoC上跨过器材逻辑阵列的数据流

主动将PCIe接口衔接到存储器

在现在的FPGA中,规划人员在将高速接口衔接至连有FPGA的存储器材进行读写时,有必要考虑在器材内因为衔接逻辑、进行布线、以及输入和输出信号的方位而发生的推迟。为了完结根本的接口功用,在规划过程中构建一个简略的存储接口一般就要花费很多的时刻。

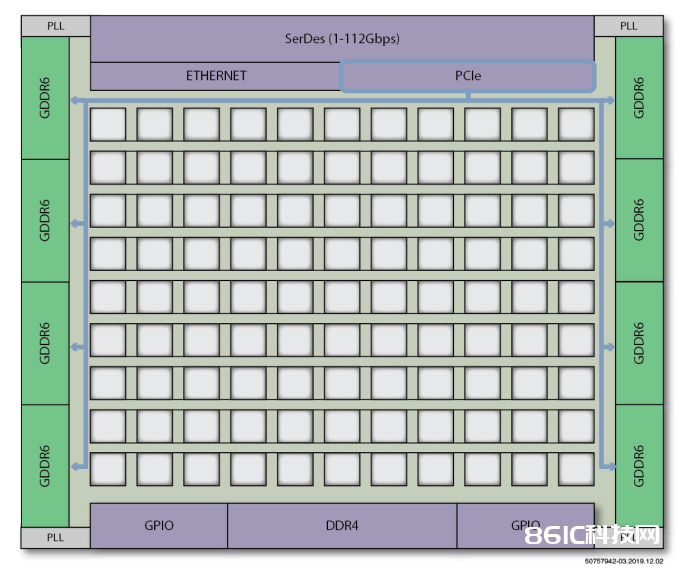

在Speedster7t架构中,将嵌入式PCIe Gen5接口衔接到已衔接的GDDR6或DDR4存储器这项作业,可由外围NoC主动处理,不需求规划人员编写任何RTL来树立这些衔接。因为NoC衔接到一切的外围IP接口,因而规划人员在将PCIe衔接到GDDR6或DDR4的任何一个存储器接口时,都具有极大的灵敏性。鄙人面的示例中,NoC能够供给满足的带宽,以继续支撑PCIe Gen 5通讯流衔接到GDDR6内存的恣意两个通道。这种高带宽衔接无需耗费任何FPGA逻辑阵列资源即可完结,而且规划所需时刻简直为零。用户只需求启用PCIe和GDDR6接口即可在NoC上发送业务。

图3:将PCIe直接衔接到GDDR6接口

在独立的FPGA逻辑阵列模块上完结安全的部分重新装备

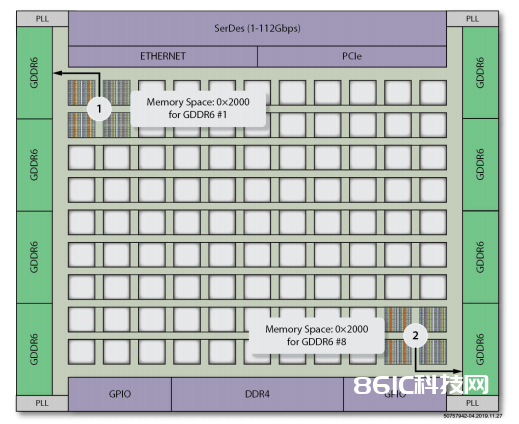

与其他根据静态随机存取存储器(SRAM)的FPGA相同,Speedster7t FPGA有必要在通电时进行装备。Speedster7t FPGA具有一个片上FPGA装备单元(FCU),用于办理FPGA的初始装备和任何后续的部分重新装备。FCU还被衔接到NoC,然后在装备FPGA时供给了更高的灵敏性。运用NoC将装备位撒播输到Speedster7t FCU,能够运用曾经不可用的新办法来对FPGA进行装备。

在器材装备之前,Speedster7t NoC可用于某些读/写业务:PCIe至GDDR6、PCIe至DDR4、最终是PCIe至FCU。一旦PCIe接口被设置好,FPGA就能够经过PCIe接口接纳装备比特流(bitstream),并将其发送给FCU以装备器材的其余部分。一旦抵达FCU,装备比特流被写入FPGA可编程逻辑以装备器材。在器材被装备完结后,规划人员能够灵敏地重新装备FPGA的某些部分(部分重新装备),以增加新的功用或进步加快功用,而无需封闭FPGA。

新的部分重新装备比特流能够经过PCIe接口发送到FCU,来重新装备器材的任何部分。当部分器材被重新装备时,经过在所需的区域中实例化一个NAP与NoC进行通讯,任何进出新装备区域的数据都能够在Speedster7t1500器材中被轻松拜访。NoC消除了传统FPGA部分重新装备的复杂性,因为用户不用忧虑环绕现有逻辑功用进行布线并影响功用,也不用忧虑因为该区域中的现有逻辑而无法拜访某些器材的引脚。该功用节约了规划人员的时刻,并在运用部分重新装备时供给了更大的灵敏性。

此外,部分重新装备答应规划人员在作业负载改变时调整器材内的逻辑。例如,假如FPGA正在对输入的数据履行紧缩算法,而且不再需求紧缩,则主机CPU能够告知FPGA重新装备,并加载经过优化的新规划以处理下一个作业负载。在器材仍处于运转状况时,部分重新装备能够在逻辑阵列集群(cluster)级别上独立完结。一个聪明的用例是开发一个具有自我感知的FPGA,该FPGA经过运用一个软CPU来监测器材操作以实时发动部分重新装备,来封闭逻辑然后节约功耗,或在FPGA架构中增加更多加快器模块,以暂时处理很多的输入数据。这些功用为规划人员供给了史无前例的装备灵敏性。

图4:运用Speedster7t NoC完结硬件虚拟化