第四章DSP芯片的衔接与装备

DSP(Digital Signal Processor)作为可编程数字信号处理专用芯片是微型计算机开展的一个重要分支,也是数字信号处理理论实用化进程的重要技能东西。跟着微电子技能和数字信号处理技能的飞速开展,DSP的功用价格比不断提高,并因为其体积小、成本低、易于产品化、可靠性高、易扩展及便利地完结多机分布式并行处理等功用,在产品开发和科学研究的各个领域获得了越来越多的广泛使用。

DSP的特色首要有以下几个方面:

◇高速、高精度的运算才能

DSP的实践使用所面临的最杰出的问题便是算法的实时完结问题。不管模仿硬件功用的实时数字化软件完结,仍是特别算法的实时处理等,都要求高速、高精度的运算才能。因而,一般DSP都具有较快的指令履行周期、并行的内部指令履行流水线,以及内部集成的硬件乘法器,使运算速度更快、运算精度更高。

◇强壮的数据通讯才能

数字信号处理往往触及较大的数据吞吐量,因而,DSP都具有DMA、串行/并行以及多CPU之间的通讯方法。

◇灵敏的可编程性

通用DSP完全是经过编程来完结数字信号处理功用,因而,DSP装备片内RAM和ROM,也可便利地扩展程序、数据及I/O空间。一起,答应ROM与RAM之间的直接数据传送。时钟频率可经过内部锁相环电路调理。体系各种特性的器材软硬件操控为编程的便利灵敏供给了充沛的空间。

◇低功耗规划

DSP能够作业于省电状况,节省了动力。

现在,DSP的开展十分敏捷。硬件结构方面首要是向多处理器的并行处理结构、便于外部数据交换的串行总线传输、大容量片上RAM和ROM、程序加密、添加I/O驱动才能、外围电路内装化、低功耗等方面开展。软件方面首要是归纳开发渠道的完善、使DSP的使用开发愈加灵敏便利。以下咱们将对本项目中所选用的DSP芯片和某些所用到的芯片重要引脚的具体衔接方法以及DSP地址空间的分配作具体的介绍。4.1 TMS320VC5416介绍

本项目中,咱们选用了TI公司型号为TMS320VC5416的数字信号处理芯片。该芯片是16位定点DSP.它选用批改的哈佛结构,程序与数据分隔寄存,内部具有8条高度并行的总线。片上集成有在片的存储器和在片的外设以及专门用处的硬件逻辑,并配备有强壮的指令体系,使得该芯片具有很高的处理速度和广泛的使用适应性。再加上选用的模块化规划以及先进的集成电路技能,芯片功耗小,成本低,自推出以来已广泛使用于各种专门用处的实时嵌入式体系和仪器中。下面临该芯片的结构体系与要害特性予以简略的介绍。

它的硬件结构基本上分为3大块:

1. CPU

●先进的多总线结构,具有1条程序存储器总线、3条数据存储器总线和4条地址总线。

●40位的算术逻辑单元(ALU),包含2个独立的40位累加器、40位移位寄存器

●2个地址生成器

●17×17Bit的并行乘法器

2.存储器体系:

●16K×16Bit的片内程序ROM

● 128K×16Bit的片内RAM,包含8块8K×16Bit的片内双拜访DARAM和8块8K×16Bit的片内单拜访SARAM. 3.在片的外设与专用硬件电路:

●16位可编程定时器

●3个多通道缓冲串口(McBSP)

●8/16Bit并行主机接口

●在片的锁相环时钟发生器

别的,还具有契合IEEE1149.1规范的在片仿真接口,可与主机衔接,用于开发使用体系芯片的仿真。

4.2芯片引脚衔接方法

本节将结合实践项目中引脚的具体衔接方法对TMS320VC5416某些重要的引脚作具体的介绍。

4.2.1数据信号引脚

1.地址信号线A[22..0]

地址信号线的A15~A0能够寻址外部程序、数据空间和I/O空间。而地址线的高7位A22~A16是专门用来寻址外部程序空间。

2.数据线D[15..0]

数据线是CPU核与外部程序、数据空间和I/O空间之间数据传送的通道。

4.2.2初始化、中止、复位操作引脚

1.用户输入中止引脚INT[3..0]

该引脚为输入引脚,低电平有用,是专门为用户设置的外部中止输入。这些中止能够经过对中止屏蔽寄存器IMR的设置来调整它们的优先级和决议是否屏蔽该中止。项目中咱们选用了INT0、INT1、INT2这三个中止通道。

2.不行屏蔽中止引脚NMI

该引脚也是专门为用户设置的外部中止输入,低电平有用。但它与INT[3..0]的区别是:NMI是不受IMR屏蔽寄存器影响的,它是不行屏蔽中止。项目中,咱们直接把它接为高电平。

3.复位引脚RS

该引脚为输入引脚,低电平有用。当复位引脚有用时,DSP中止履行程序,强制程序指针指向0FF80h.项目中,该复位信号由FPGA2供给。

4.作业方法挑选信号引脚MP/MC

DSP有两种作业形式:微型处理器形式和微型计算机形式。当MP/MC置为高电平时,微处理器形式被挑选;低电平时,微型计算机形式被挑选。当作业在微型计算机形式下时,DSP片内ROM映射到程序空间的高16K字地址;作业在微处理器形式时,片内ROM不映射到程序空间。项目中,咱们在DSP上电复位时,将MP/MC设置为高电平,让它处在微处理器作业形式,直接从外部FLASH的0FF80h地址开端履行程序。该程序模仿DSP内部的Bootloader功用:首要从头设置PMST、ST0、ST1等DSP装备寄存器,并将自己复制到内部RAM中持续运转;然后再将用户的主程序、用户设定的中止向量表从外部FLASH复制到内部RAM中,第三步将DSP的作业形式设置为微型计算机作业形式,并且在程序终究远跳转到地址1FF80h处,而该地址正是内部RAM保存的用户设定的中止向量表开始地址,在该处又有一条跳转指令使得程序终究跳转至用户主程序的开始地址。

4.2.3通用I/O端口引脚

1.外部标志输出引脚XF

该引脚为输出引脚。项目中,咱们首要用此引脚来完结DSP,FPGA2分时占用SRAM3地址和数据总线的操控信号。

4.2.4存储器操控信号引脚

1.数据、程序、I/O空间挑选信号引脚DS、PS、IS

DSP的数据空间、程序空间、I/0空间是分隔的。当DS为低电平时,数据空间被挑选;PS为低电平时,程序空间被挑选;IS为低电平时,I/O空间被挑选。项目中,这三个挑选信号首要与DSP输出的地址信号合作,发生相应空间外部扩展的挑选信号。

2. DSP读写信号引脚R/W

此信号首要表明当DSP与外部器材进行数据交换进程中数据的传送方向。

3.外部数据存储器选通讯号引脚MSTRB

当有外部总线拜访数据和程序空间时,该信号为低。项目中,该信号与DSP的读写信号合作发生外部扩展数据和程序空间的读写信号。

4. I/O设备选通讯号引脚IOSTRB

当外部总线拜访DSP的I/O空间时,IOSTRB为低电平。项目中,该信号与DSP的读写信号合作发生外部I/O空间的读写信号。

5.时钟输入引脚X2/CLKIN

当不选用DSP内部时钟信号时,此引脚作为外部时钟的输入引脚。项目中,咱们在此引脚加上了10MHz的规范频率信号。

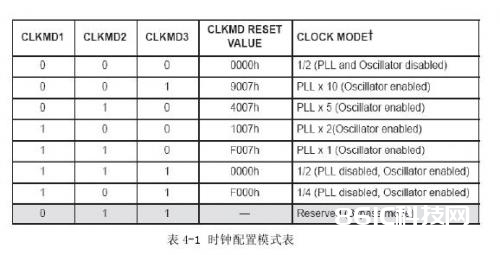

6.时钟形式挑选引脚CLKMD1、CLKMD2、CLKMD3

DSP有内部时钟、外部时钟、PLL三种时钟形式。这三个引脚首要用来在DSP复位时初始化时钟形式挑选寄存器。寄存器中的内容界说了时钟的装备形式。具体的装备形式如表4-1.

项目中,咱们选则第三种装备方法,即CLKMD1、CLKMD3接为低电平,CLKMD2接为高电平。

4.2.5多通道缓冲串行接口(McBSP)

TMS320VC5416中共有3个多通道缓冲串行接口,它首要完结DSP与配套外设之间的串行通讯。它包含的引脚有:

1.接纳串行数据时钟信号BCLKR

它首要为DSP接纳外部串行数据时供给数据搬运时钟。

2.接纳串行数据线BDR

它是外部串行数据输入端。

3.接纳串行数据帧同步信号BFSR

它首要的作用是确保接纳串行数据的同步。

4.输出串行数据时钟信号BCLKX

它首要为DSP向外输出串行数据供给数据搬运时钟。

5.输出串行数据线BDX

它是串行数据输出端。

6.输出串行数据帧同步信号BFSX

它首要确保输出串行数据的同步。

(有关串行通讯的内容咱们将在第六章《串行接口通讯》做具体的介绍。)

除了上述的引脚外,DSP还有测验引脚、主机接口引脚等。测验引脚是契合IEEE1149.1规范的在片仿真接口,首要是完结DSP的实验仿真。主机接口引脚首要是完结DSP与PC或其他主CPU间的通讯。项目中,咱们没有用到主机接口引脚。