电路功能与优势

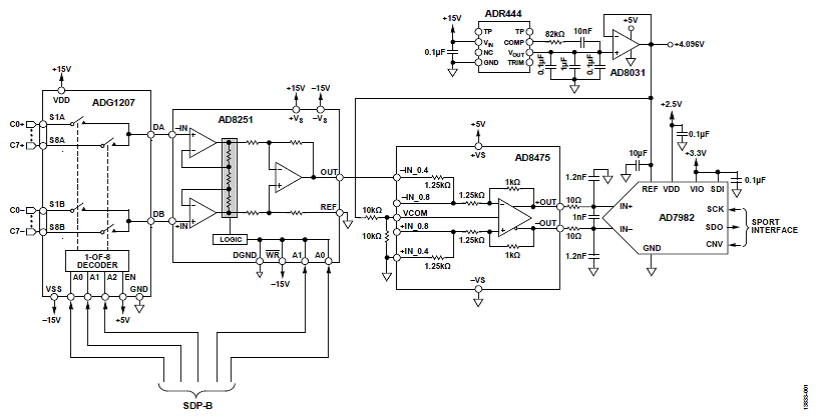

图1所示电路是高性价比、低功耗、多通道数据收集体系,兼容规范工业级信号。元件针对两次采样之间的最佳树立时刻而挑选,能以高达约750 kHz的通道切换速率供给18位功能。

该电路能够处理八个增益独立的通道,兼容单端和差分输入信号。

模仿前端包含一个多路复用器、可编程增益外表放大器(PGIA)、用于履行单端转差分使命的精细模数转化器(ADC)驱动器,以及一个用于采样有用通道信号的18位、1 MSPS PulSAR® ADC。供给0.4、0.8、1.6和3.2增益装备。

体系最大采样速率为1 MSPS。通道切换逻辑与ADC转化同步,最大通道切换速率为1 MHz。单通道采样速率高达1 MSPS,分辨率为18位。通道切换速率高达750 kHz时仍然具有18位功能。体系还具有低功耗特性,在1 MSPS最大ADC吞吐速率下的功耗仅为240 mW。

图1.多通道数据收集简化电路(未显现一切衔接和去耦)

电路描绘

图1中的电路是个多通道数据收集信号链,由多路复用器、可编程增益级、ADC驱动器和全差分PulSAR ADC组成。

通道切换和增益切换与ADC的转化周期同步。体系能够运用单个ADC监控多达八个通道,比较每通道一个ADC的体系而言,减少了元件数量并下降了本钱。每通道都可装备为不同增益,为输入规模供给了灵活性。各通道的有用采样速率等于ADC的采样速率除以采样总通道数。

体系的最大采样速率受限于模仿前端元件的树立时刻。多路复用信号本质上是断续的,因而采样距离之间或许具有较大的电压阶跃。ADC履行转化前,信号链上的元件必须有满足的时刻树立至这些阶跃。为使信号树立时刻最大化,多路复用器通道会在ADC开端新的转化之后当即切换。

元件挑选

ADG1207是一款低%&&&&&%、快速树立多路复用器,可将8个差分输入之一路由至公共差分输出。ADG1207输入端的切换网络能为单端和差分输入信号供给兼容性。有用通道经过器材地址引脚挑选,由SDP-B操控器板操控。

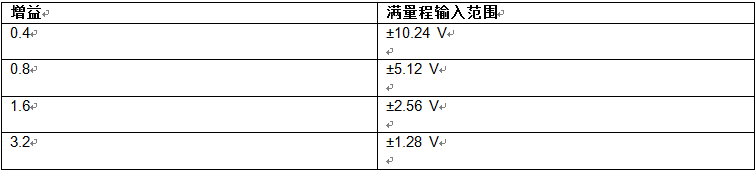

AD8251是一款可编程增益外表放大器,供给1、2、4和8可选增益设置。较高的增益设置使较小的输入信号升压至AD7982的满量程输入规模内。每一个增益设置都有自己的适宜输入规模,如表1所示。

表1.四个增益

装备的输入规模

AD8475漏斗放大器供给高精度衰减(0.4×)、准确的共模电平转化以及单端至差分转化。该器材具有低输出噪声频谱密度(10 nV/√Hz)和快速树立时刻(树立至0.001%:50 ns,2 V输出阶跃),十分合适用来驱动AD7982。

AD7982是一款全差分、1 MSPS、18位PulSAR ADC,运用4.096 V基准电压源时的典型SNR为96 dB。AD7982相同具有低功耗特性,最大吞吐速率时的功耗仅为大约7 mW。该器材的功耗随吞吐速率而变,可在较低采样速率下作业以下降功耗(例如,10 kSPS时功耗等于70 μW)。

体系直流精度差错

图2显现了数据收集体系的抱负传递函数。

图2.ADC抱负传递函数

数据收集信号链上的每一个元件都存在差错,导致体系的实在传递函数与图2有所不同。这些差错的累积效应能够经过比照ADG1207输入端的直流输入和AD7982的输出码而在体系级进行丈量。该体系的方针差错是失调差错和增益差错。

失调差错丈量

关于抱负的双极性、差分ADC而言,0 V差分输入的输出码为0。真实的ADC一般会有一些失调差错(εb),其界说为抱负输出码与0 V输入的丈量输出码之间的差错。

数据收集体系的失调差错能够经过将其输入接地,然后调查输出码而找出。此差错在AD8251的各增益设置下均有所不同,而且ADG1207各通道之间也有所不同。因而,在悉数四种增益装备下对各通道进行失调差错丈量。

因为体系监控多个通道,对通道之间的失调差错进行量化也很重要。失调差错匹配(Δεb, MAX)用来衡量各通道的失调差错以及一切通道的均匀失调差错之间的差错。运用下式核算失调差错匹配:

其间,εb,i和εb,j别离表明i和j通道的失调差错。

每一种增益装备都存在失调差错匹配。留意,失调差错能够表明为码,也能够表明为电压(伏特)。

增益差错丈量

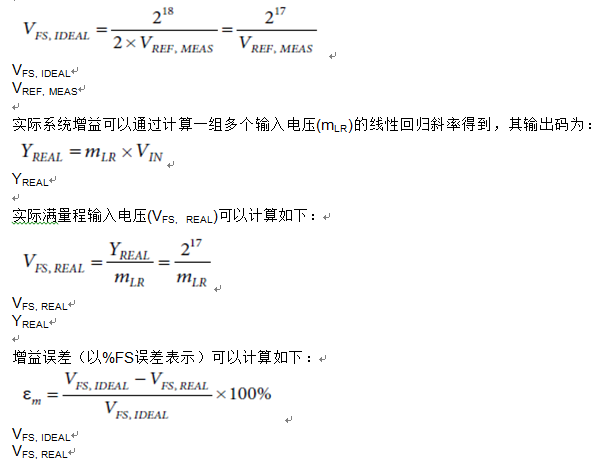

体系增益差错也会使整个体系具有不准确性。AD7982的抱负传递函数如图2所示,其间−217和217 − 1输出码别离对应负满量程输入电压(−FS)和正满量程输入电压(+FS);但是,失调差错(εb)和增益差错(εm)的组合却会导致此联系发生差错。

增益差错能够表明为实践体系增益和抱负体系增益之间的百分比差错。更为常见的表明办法是选用百分比满量程差错(%FS),它衡量发生217 − 1码的抱负和实践输入电压之间的差错。

抱负满量程输入电压(VFS, IDEAL)与ADC分辨率(AD7982为18位)以及基准电压(VREF)的精度成函数联系。基准电压差错会导致ADC的增益差错。为了去耦基准电压差错与ADC增益差错,运用精细万用表丈量VREF。然后便可运用下式核算抱负满量程输入电压:

体系增益差错随AD8251增益而变,但各通道独立。因而,增益差错针对四个增益装备别离进行丈量,但在体系中仅运用ADG1207的其间一个通道。

体系噪声剖析

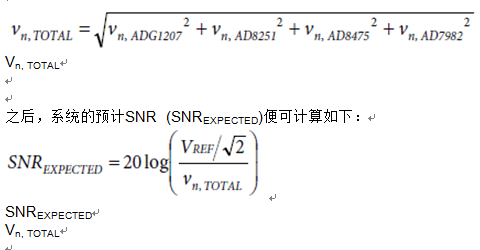

精细数据收集体系的要害规划方针之一是完成高信噪比(SNR),这能够经过添加满量程信号起伏和/或下降体系中元件发生的噪声功率完成。

体系中的总噪声功率能够经过元件各自的噪声功率折合到AD7982输入端的和方根(rss)核算得出:

体系中各元件的估计噪声奉献以及整个体系的估计SNR功能如表2所示。在总体系噪声核算时,疏忽体系中无源元件的热噪声奉献。