IEEE-1394b总线协议具有实时性、可靠性、确定性等特性,这些特性使其在点对点通讯方面体现杰出。IEEE-1394b作为F22猛禽战机的总线,一起也运用在F35、NASA的航天飞机上以及DV设备上。而总线的仿真验证设备需求图形化的界面软件,这就要求其作业环境支撑PC机环境。作为硬件与软件桥梁的驱动程序首要作业是确保软硬件和谐作业,供给安全简略的操作接口,确保通讯数据的可靠性、实时性、确定性等。

1 硬件体系简介

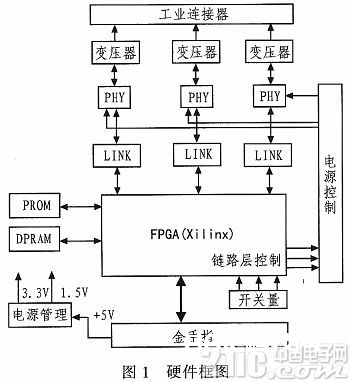

图1是以Xilinx的V6系列的FPGA为中心的硬件框图。该设备具有3个余度,而且三余度之间可以独立作业,互不影响。硬件选用三路Link和PHY芯片,三路独立供电。因为仿真设备运转的环境的封闭性,然后规划软件和硬件两种供电操控开关。软件电源操控信号由FPGA操控可编程的电源操控芯片来长途操控设备。设备供电无需外接电源,直接运用PC机的PCI或许PCIe总线插槽供电,硬件供给电源办理体系进行电压转化。该设备支撑速率S100Mbps和S400Mbps,硬件供给S100Mbps和S400Mbps端口速率切换按钮,FPGA内部通讯速率由逻辑操控完结。

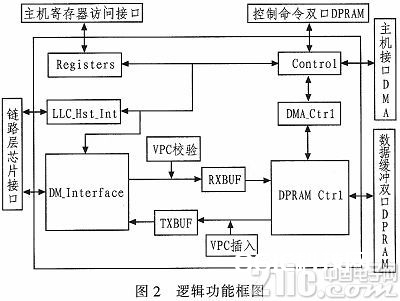

FPGA逻辑功用框如图2所示,FPGA逻辑对PCI/PCIe总线协议和1394b总线进行协议封装以及协议解析;对内存空间,IO空间以及中止号等进行区分;对操作寄存器进行界说;对发送数据的DM口,接纳数据的GRF口进行操控;敞开LINK和PHY的软件拜访权限,便于完结长途拜访功用;对DPRAM进行双口切换操作,以确保数据通讯的可靠性;规划退避算法防止总线竞赛失利数据丢掉;支撑DMA操作,完结通讯的实时性。

2 驱动规划

驱动程序是硬件厂商依据硬件作业环境的操作体系编写的配置文件,其运转于操作体系内核态,是设备与计算机交互的桥梁,它把硬件的功用告知操作体系,一起也将体系

的指令传达给硬件。驱动软件分为软件驱动和硬件驱动。软件驱动是把作业终究交给CPU处理,对CPU依赖性比较高,对操作体系影响比较大;而硬件驱动可以最大化的防止CPU的调度,进步硬件资源的运用率、添加传输的实时性、削减设备对计算机的依赖性等。

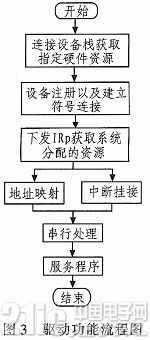

本设备驱动程序选用硬件驱动,开发东西为DDK(Device Development Kit),调试东西为Debug view,其作业流程如图3所示。

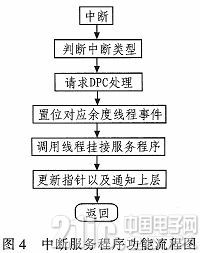

因为Windows是多使命非实时的操作体系,每个进程占用处理器的时刻应小于50微秒,假如需求长时刻的硬件拜访应选用体系线程的办法,本规划选用三余度三个内核线程对数据处理用以确保拜访的准确性。因为该设备硬件的方便性和软件的延时性,而且突发大数据量传输发生概率比较高。所以驱动程序在发送模块上运用了乒乓原理,在接纳模块运用了循环行列,确保数据可以滑润的通讯,在突发大数据量操作时确保了数据的完好性和确定性。因为中止函数(wdmISR)的体系优先级最高,其作业占用CPU资源可以影响到整个体系的运转,所以中止需尽或许的简略、尽或许防止运用浮点操作、尽或许的将处理移交给使命处理。所以规划了中止延时处理函数DPC(Deferred Procedure Call)对体系进行资源合理运用确保通讯的有用性。中止服务程序功用框图如图4所示。

串行处理:为了进步硬件资源运用率以及设备作业的安全性。本设备规划为三余度(两个余度为主节点,一个余度为备用节点)一体设备,三节点可以独立进行作业。1394b总线协议答应发送物理层包拜访长途节点,而且可以经过长途拜访包对设备节点进行长途操控。所以当恣意一个主节点呈现毛病,备用节点可以经过长途指令断开毛病主节点,然后启用备用节点,添加设备运转的安全性。

单功用多设备的运转对驱动程序而言每个设备都有自己的内存空间、I/O空间以及中止号,运转互不影响。软件对硬件的操作,在串行处理方面只需求对操作进行排队处理,就可以防止软件对硬件的并行操作。而三余度多功用多样性设备的运转对驱动而言,运用的或许有许多的共享资源(如DMA等资源),而且软件对3个余度的操作有或许是并行的,驱动软件规划在节点间共享资源进行加锁处理确保通讯的独立性及确定性。

串行处理可以有用的防止资源拜访抵触,可以以不同优先级等级操控各个功用,可以以不同频率操控各个功用,有用的进步了软件对硬件操作的安全性。该驱动规划了节点间公共资源拜访设置互斥信号量(KeWaitForMultipleObjects),只要信号的具有者才干开释信号量。一起规划了维护节点内共享资源的维护措施,如中止挂接IoCionnect Intei Tupt函数下的自旋锁。对上层操作进行仓库处理,确保操作的有用性,而且对该操作进行危险评价(如对链路层操作或许影响设备收发数据操作),抵达对硬件的全面维护。

内核线程:因为该设备应用于通讯方面,突发性大数据量传输发生率比较高,而windows环境下每个进程占用处理器的时刻应小于50微秒,所以该驱动在PNP(Plug and Play)

为每个节点设置一个线程(PsCreateSvstemThread)对突发的大数据量数据进行滑润处理,以确保数据平稳的交由上层,该线程为事情驱动类型。而且经过KeCetCurrentThread和KeSetPriorityThread调整线程优先级。

当中止发生,中止处理函数记载中止状况并铲除中止,判别中止是否为空,假如不为空则经过IoRequestDpc恳求DPC,一起把相应的中止状况传给DPC。DPC经过中止状况判别中止类型和发生中止的节点,而且置位对应线程的线程事情。线程触发后,从堵塞态变为安排妥当态,当该进程得到处理器资源,调用数据处理函数处理数据。

DMA:Windows是多使命非实时的操作体系,而DMA可以有用的防止CPU的调度而节省时刻,进步设备的实时性。体系要求DMA的运用率尽或许的削减而且尽或许的方便。本规划运用硬件侧DMA,由FPGA逻辑完结,DMA操控由驱动操控。

驱动软件对DMA进行初始化,当中止服务程序被调用,驱动程序依据DPRAM的0、1区标志获取新数据寄存区域,并从该区获取新数据的改写符号。如有新数据,则服务程序请求DMA资源,获取到DMA资源后,确定DMA资源并发动(DMA源地址、意图地址、数据搬运长度、操控指令)I/O端口到主存区的DMA。DMA完结后上报完好中止并开释DMA资源。当上层调用IRP_MJ_DEV%&&&&&%E_CONTROL对DPRAM进行写操作时,驱动程序判别用户该次操作的DPRAM的内存大小,假如在32K~2048K字节之间,则发动主存区到I/O端口的DMA,假如大于则分次发动DMA,假如小于32K字节则单拍或许多拍操作。操作流程与发动接纳DMA相同,操作完结则上报中止。

循环行列:方便性是硬件的特性之一,而应用层相对于硬件是及其缓慢的。而且因为PCI数据包封包的影响,其总线实践带宽只要133 Mbps/s,而本1394b设备支撑S100Mbps

和S400Mbps两种传输速率。所认为防止设备长时刻作业带来内存递加、内存走漏以及突发大数据量给PCI总线通讯超负荷运转形成数据丢掉现象,驱动运用IoAllocateMdl请求一块3M的内存区,供硬件软件交互循环运用的循环行列用以确保传输的有可靠性,以及安全性。

当中止服务程序被调用时,驱动发动DMA或许读写寄存器操作把数据从指定DPRAM区搬运到主存区,更新新的数据指针并经过软中止方法告诉上层软件。上层软件经过Deviee IoCo ntrol对设备进行操控,当应用层对驱动进行操作时,驱动依据写指针与读指针的差值供给可操作的内存块给上层软件。

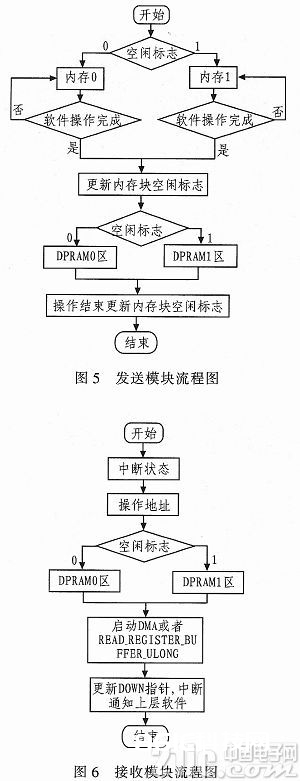

乒乓原理:乒乓原理不只可以进步带宽的运用率,而且可以有用防止硬件与软件操作抵触状况的呈现,而且防止了资源拜访抵触的重试耗时,进步传输的有用性、实时性。驱动收发模块乒乓操作如图5和图6所示。

发送模块中,驱动软件与应用层交互,选用两块地址内存区。内存块操作由用户层软件操作,操作完结后切换内存区并告诉驱动最新数据寄存方位。驱动软件与硬件交互也选用两块DPRAM区。DPRAM的0、1区的切换操作由驱动软件进行操作,数据更新结束的DPRAM交由逻辑处理并进行换区操作。

接纳模块中,驱动软件规划循环行列与上层软件进行交互。硬件与驱动软件交互相同选用乒乓原理,该操作由硬件逻辑操作,驱动软件依据最新数据寄存的DPRAM区,以及消

息新旧符号来进行数据处理。处理完结后完结数据新旧标志切换,并软中止方法告诉应用层有新数据抵达,应用层驱动回来的地址指针和内存大小获取最新数据。

3 验证剖析

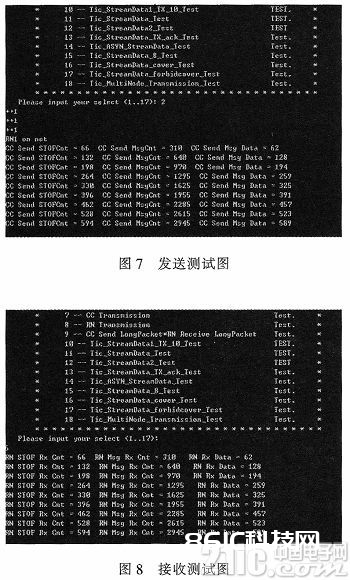

本设备供给DLL(Dynamic Link Library),选用Microsoft Visual Studio 2008专业版开发,封装为规范的动态链接库。供给Demo程序,图7为CC(Control computer)的发送数据窗口测企图,图8为RN(Remote Node)的接纳数据的窗口测企图。

由上图可见驱动程序完结了1394b的S400 Mbps速率和PCI的S133 Mbps速率的跨速率通讯数据不丢掉,防止了软硬件交互发生的误码,使在S100 Mbps通讯速率下均匀带宽抵达79.2 Mbps,在S400Mbps通讯速率下均匀带宽抵达231.7 Mbps,完结了数据延时操控在us等级,完结了操作的准确性,确保了数据传输确实定性。

4 结束语

自2011年我国面临着国外大规模技能搬运封闭以来,国内自研设备百家争鸣,尤其是软件硬化无疑已经成为焦点。作为硬件魂灵的驱动程序越来越遭到人们的注重。本文依据软硬件的特性进行软硬件作业和谐,进步了硬件资源的运用率,进步了仿真通讯的实时性,确定性,可靠性。因为需求要求该设备为PCI总线设备,通讯的带宽遭到限制,所以预备运用PCIe总线和实时操作体系进步设备的通讯带宽。