一段时间以来,MathWorks一向主张运用Matlab和Simulink开发东西进行根据模型的规划,因为好的规划技能使您能够在更短的时间内开发更高质量的杂乱软件。根据模块的规划采用了数学和可视化的办法,经过整个开发过程中运用的体系级建模(从初始规划到规划剖析,仿真,主动代码生成、开发和验证)来开发杂乱的操控和信号处理体系。这些模块是由框图,文本程序和其他图形元素组成的可履行规范。根据模型的规划鼓舞比照其他规划办法更广泛的规划空间的快速探究,因为您能够在规划周期的前期更快地迭代规划。并且,因为这些模型是可履行的,所以验证成为每一步开发过程中不可或缺的一部分。

面向英特尔® FPGA 的 DSP Builder 是一款数字信号处理 (DSP) 规划东西,经过MathWorks* Simulink* 环境中,对英特尔 FPGA 的支撑, 经过按下不同按钮生成 DSP 算法的 HDL 代码。该东西可运用 MATLAB 函数和 Simulink 模型生成可组成的优质 VHDL/Verilog 代码。生成的 RTL 代码可用于英特尔 FPGA 编程,广泛适用于雷达规划、无线和有线通讯规划、医学成像和电机操控等运用。

该东西在现有的 Simulink 库中添加了额定的库块,其间包含面向英特尔 FPGA 的 DSP Builder 高档模块集和面向英特尔 FPGA 的 DSP Builder 规范模块集。主张运用面向英特尔 FPGA 的 DSP Builder高档模块集进行全新的规划。

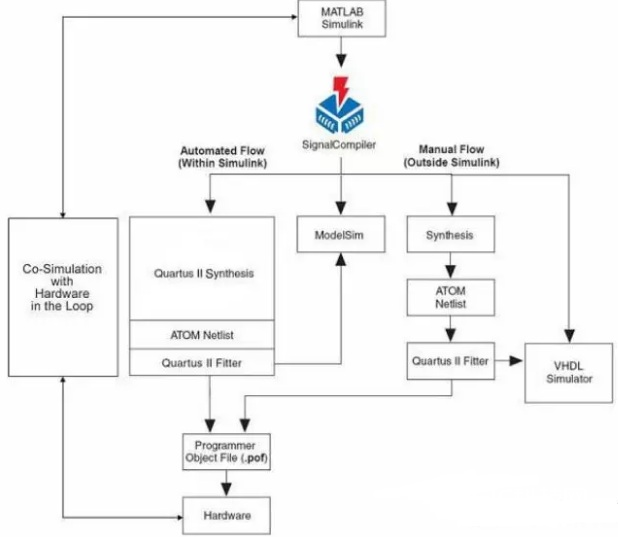

下图所示为Intel FPGA DSP Builder 体系级规划流程。

首要特性:

从高等级的示意图到针对英特尔 FPGA 优化的低等级 VHDL

运用矢量处理来履行高性能的定点和浮点 DSP,例如杂乱的 IEEE 754 单精度浮点

将规划一键迁移到英特尔 Arria® 10 和英特尔 Stratix® 10 设备上的英特尔的硬浮点 DSP 模块。

经过 ALU 折叠从扁平的数据速率规划中构建定制的 ALU 处理器架构

高档组成优化,主动流水线刺进和平衡,以及方针硬件映射

灵敏的“白盒”快速傅立叶改换 (FFT) 东西包,具有敞开的库和模块层次结构,可支撑用户构建定制的 FFT

运用规划人员拟定的体系时钟束缚主动完成流水线、时分多路复用/分折和时序收敛

拜访高档 math.h 函数和多通道数据

为一切规划生成资源利用率表,而无需运用英特尔 Quartus Prime 软件进行编译

主动为英特尔 Quartus Prime 软件、TIming Analyzer、Platform Designer(原 Qsys)以及 ModelSim-Intel FPGA 版别生成项目或脚本。