做了三年四个项目最近才第一次需求深化的搞一下FPGA 烧写。在这里简略总结一下FPGA烧写的详细进程和玩的把戏

咱们常用的办法

关于大部分人来说,至少入门时会用到的烧写办法就两种:

① 经过JTAG直接将bitsteam 烧录到FPGA。 断电后信息丢掉。这种办法多用于发开调试阶段,板子一向连着电脑。经过ISE 或许 Vivado (2020年开端估量还有Vitis)运用JTAG接口烧录。

② 在规划release今后,到产品上一般都是把装备文件经过IDE东西保存存在Nor Flash里。上电后主动编程FPGA。

较为进阶的一种办法

一般状况下这两种办法也就能够满意大部分需求了。开发调试直接JTAG。产品出货前,装备文件经过JTAG接口,用VIVADO或许SDK等东西烧进Flash。之后把接口封起来。产品需求更新的时分,派技术支持去,从头翻开接口,插上JTAG,把新的装备文件烧入Flash。

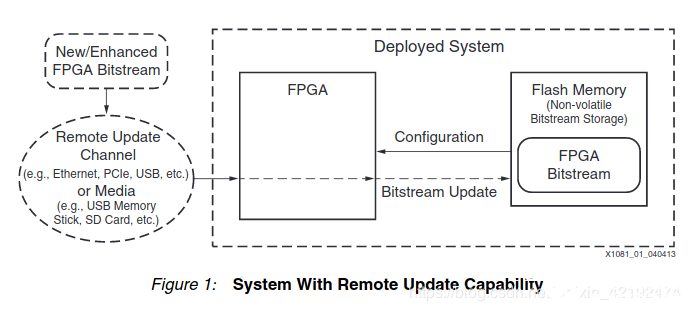

可是这次项目是个小型手持丈量设备,JTAG接口只要在设备离散状态下经过扩展板才干运用。拼装好后FPGA只能经过Flash来编程。由所以个精密仪器,每次拆开再拼装,整个设备都需求从头校准,十分费事吃力。拼装后更新Flash里边的装备文件只能用其他办法了。这种状况下常用的办法是经过一个和外界有通讯才能的微控制器将image发送给FPGA, 再由FPGA写入Flash。

这种remote update Xilinx供给了一种解决计划,相对应的ApplicaTIon Note 是 :

QuickBoot Method for FPGA DesignRemote Update (文档号码XAPP1081)

选用这种计划的条件是了解FPGA经过Flash装备的细节,所以以7系FPGA为例先需求看一下这个文档:

7 Series FPGAsConfiguraTIon (UG470) 主要是看第五章:Chapter 5 ConfiguraTIon Details

Xilinx 长途烧录FPGA办法

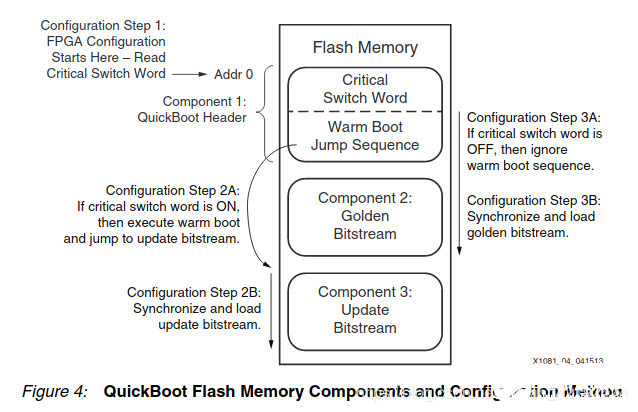

长途烧录一般是为了设备出厂今后还需对FPGA进行更新或许晋级。为了避免在烧录进程中新的装备文件损坏,导致FPGA不能正常发动。一般采纳的是双保险战略,有个gold bitstream,是出厂是写入Flash的,是测验过肯定能够发动FPGA的,还有一个是update bistream,出厂时便是一个gold bitstream的copy,FPGA每次发动都是默许写读取这个update bitstream。之后的更新也便是去重写这个 update bitstream, 一旦在更新进程出了问题,比方忽然断电。update bistream危害或许残损,FPGA在测验从update bitstream发动失利后就会去读取gold bitstream。这种办法确保了一个相对安全的update办法,所以也是一种十分经典的办法。

去掉废话来归纳这种办法

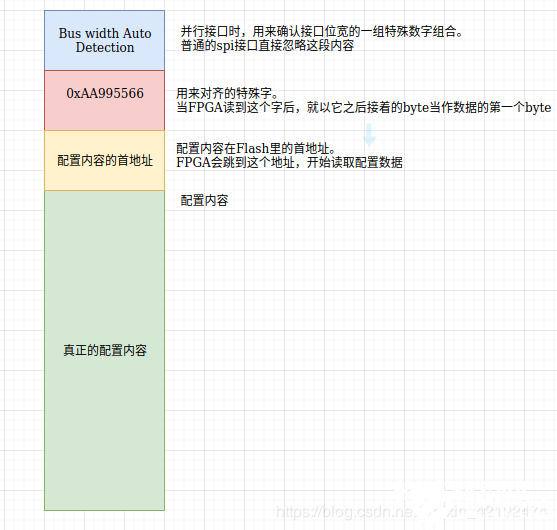

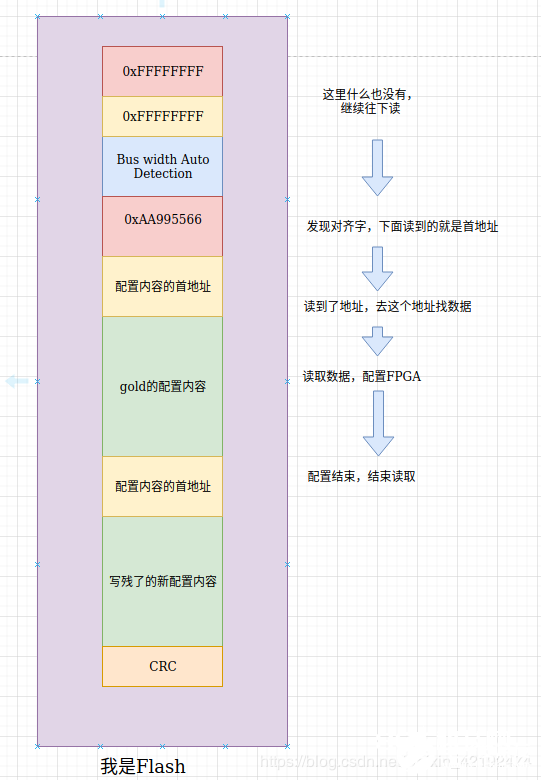

每一个bitstream都长这样:

FPGA会先去找synchro word (7系列的spi接口的话便是0xAA995566)找到今后读取首地址,然后跳到首地址,开端读取一切的装备数据。

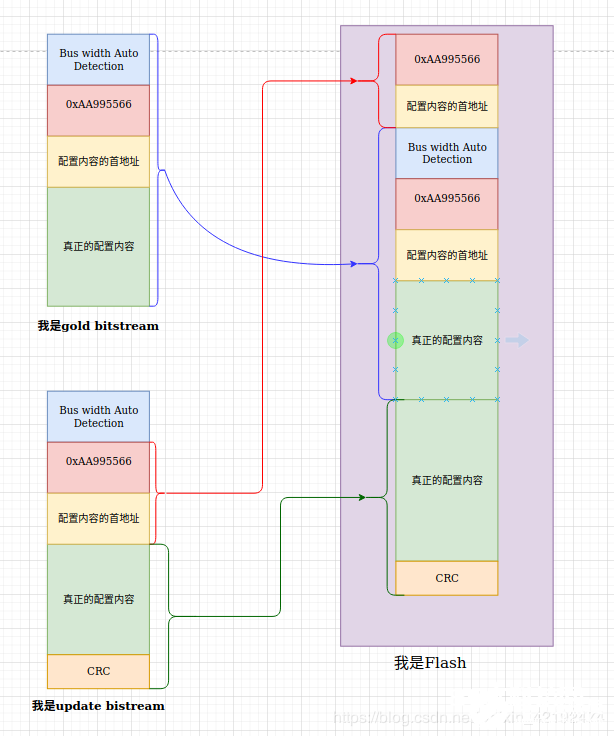

此文介绍的这种双保险战略便是在Flash中存入两个bitstream。可是精华地点是这两个Bitstream在内存中怎样放。

如下图所示,update的bitstream会被拆成两段,synchron word和首地址会被存在goldbitstream前面,然后其他部分存在goldstream之后。并且update bitsteam尾部还会人为参加一个CRC。

这种鬼畜结构的意图

这种结构能够供给一种十分安全可靠的update形式。为什么会安全可靠。先来说一下这种结构下的update流程:

当咱们想要update bistream的时分:

① 首要 update synchro word和首地址地点的sector(Flash里能够擦除的最小单元)会被擦除。

② 然后开端在update地点的当地擦除一切内容,写入新的bitstream。包含CRC。(这个CRC是生成bitstream的时分参加的。详细操作看下一章)。

③ 当写入完毕后整个新写入的内容会被读出来核算CRC,然后和嵌入的CRC来做比较。当CRC共同时,阐明在传输和写入进程没有呈现问题。新写入的装备内容完好,有用。这时update的synchro word和首地址才会写入最开端被擦除sector。

这样一来,假如CRC不共同,阐明这是个bad update,新写入的装备内容不可用。那么被擦除的synchro word 和首地址不会被写入。第一个sector是空的。当FPGA上电后,它是在这个sector里找不的update image的同步字和首地址的,继续读下去会读到归于goldbitstream的同步字和首地址。

如下图所示:

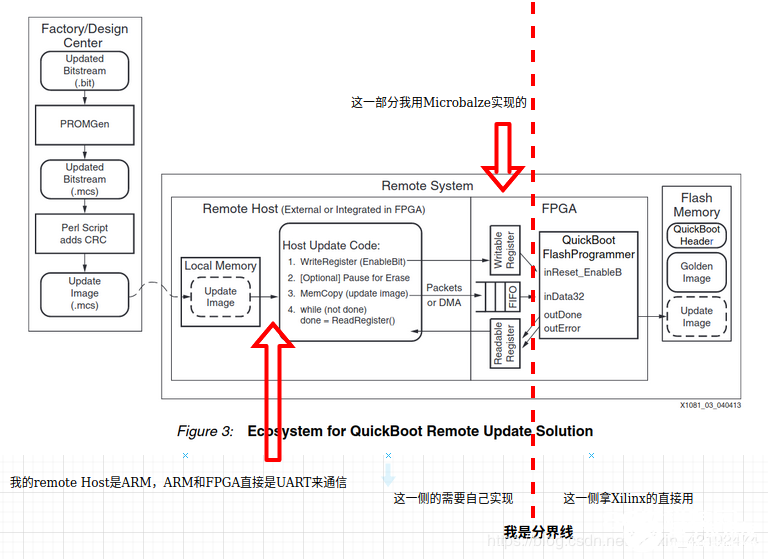

实际操作过程和文档中的坑

首要好消息是,上述的这些Flash擦除,写入,各种地址,sector,page等等Xilinx现已写好了VHDL的模块。能够直接拿来用。自己需求完成的是remote端往FPGA的数据传输。详细如下图:

详细完成过程如下:

① 完成remote端的update程序,该程序需求读取update image 然后经过某种接口和通讯协议将image发送给FPGA。这一步该需求和状况自由发挥。例如物联网的能够用蓝牙或许WIFI。

② 完成FPGA端的数据接纳。该模块将数据写入Xilinx供给的FlashProgrammer

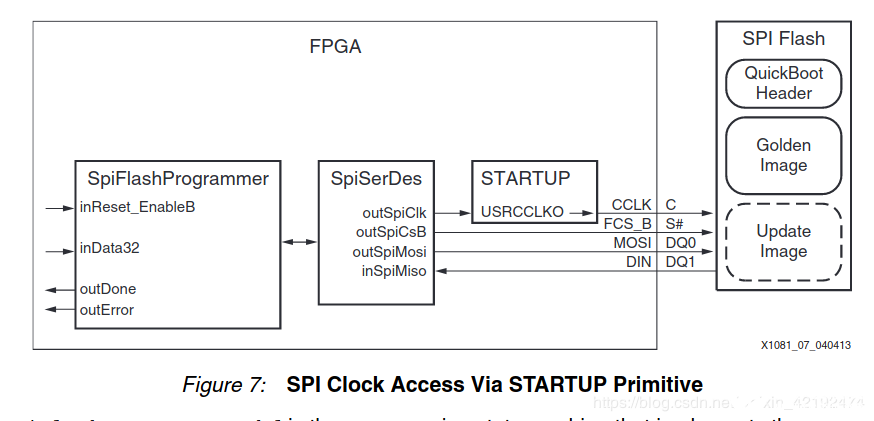

③ 下载XAPP1081文档中的比如 KC705 Board DemonstraTIons, page 33。比如中两个VHDL模块按下图实例化。留意 这两个模块有必要共用一个时钟,并且这个时钟便是SPI的时钟,所以留意不要太快。一般20Mhz一下。

④ 集成前三条完成的模块,调试。能够完成将数据从remote端发送给FPGA,经过SPiFlashProgrammer写入Flash。

⑤ 把bitstream格局转化成mcs格局。将gold bistream。bit格局转化成mcs格局。VIVADO下运用tcl 指令write_cgfmen -format mcs -interface spix1。一定要加 -interface spix1,否则一切的bits都会被swap!

⑥ 经过Xilinx比如中供给的Perl Script生成 gold init image。script的输入便是方才转化的mcs格局的goldbitstream.mcs。输出之一是gold init image这个image便是图4中描绘的那种鬼畜布局的双bitstream,只不过两个bitstream是相同的。update bitstream是gold的copy。

⑦ 将gold inital.mcs经过VIVADO 或许PROMgen用JTAG直接烧入Flash

⑧ 相同的办法用Perl Script生成 update image。 输入是xxx.mcs。输出之一是xxx_update.mcs。这个便是上文所属的加了CRC的update image。生成进程中perl script会给出Flash的首地址和完毕地址。将SpiFlashProgrammer中的首尾地址改成这两个地址。留意:由于首尾地址是写在VHDL里的,也便是说Image的巨细是固定的。为了避免在未来,update image变大。能够预留一部分出来。例如:现在的巨细是3.3MB。咱们预留0.7MB给未来或许呈现的更新。那么咱们需求生成的image需求4MB大。这是要给perl script一个附加的agrument: -imagesize 32

⑨ 将xxx_update.mcs转化成.hex文件。网上有不少东西能够。真实不可谷歌一下mcs格局,自己写个script转化一下。

⑩ FPGA上电,撤销SpiFlashProgrammer的reset。 remote的软件读取xxx_update.hex,传输给FPGA,经由SpiFlashProgrammer写入Flash。

⑪ 写入后,查看Programmer的Status. Done输出1,一切Error Port输出是0的话,阐明update成功!

⑫ FPGA从头上电,查看FPGA内是否是由新的image装备的

责任编辑:gt