1、 概 述

雷达观测的方针有大、有小,有远、有近,因而反射信号的强弱程度或许改变很大。当大方针处于近距离时,其反射信号很强,就会使接收机发生过载现象,损坏接收机的正常作业。为了防止强信号使接收机过载,需求对接收机的增益进行调理;在盯梢雷达中,为了确保对方针的主动方向盯梢,要求接收机输出的角差错信号的强度只与方针违背天线轴线的夹角D(称为差错角)有关,而与方针的远近、反射面积的巨细等要素无关(即差错信号完成归一化),因而选用主动增益操控电路(AGC)。

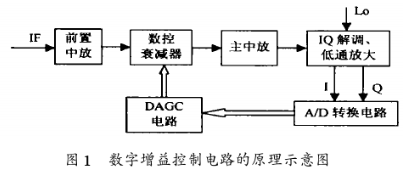

数字增益操控电路的原理图示如图1所示,其间IF是中频输入信号,Lo是相干信号。

关于单脉冲盯梢雷达而言,图1是和支路的电路框图,他是一个闭环体系,为了确保2个差支路输出的角差错信号与方针的远近无关,和路发生的AGC操控码有必要一起对2个差路进行增益操控,为了补偿和差三路的数控衰减器的不一致性,一般运用ROM来批改差路的操控特性曲线,以和路AGC操控码为地址,ROM内的数据是和路AGC操控码所对应的差路AGC操控码。

2、 用CPLD器材完成DAGC运算

由ALTERA公司所推出的杂乱可编程逻辑器材(CPLD)有各种系列的产品。其间EPFl0K系列集成度到达了上万门,并含有较大容量的内部存储器,能够在单个器材内集成很多的功用单元,完成杂乱的逻辑电路。

VerilogHDL是在运用最为广泛的C言语基础上发展起来的一种硬件描绘言语,VerilogHDL供给了十分精简和易读的语法,相比较而言,VHDL的描绘长度是VerilogHDI。的2倍。规划者只需学会Verilog一门言语,就能够敷衍逻辑规划中一切方面的作业。

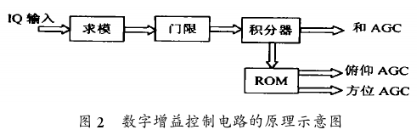

IQ解调扩大后的零中频模仿信号经A/D转化电路变成数字信号至DAGC电路,DAGC电路选用单片CPLD器材(EPFl0K100EQC240-1),器材内部的运算悉数选用VerilogHDL言语编程完成,子程序包含:求模运算、门限、积分器及时序电路。DAGC电路的内部逻辑图如图2所示。 求模运算相当于传统模仿AGC电路中的峰值检波器,一般有2种办法可完成求模运算:一种是查表法;另一种是选用经历公式来核算。为了简化程序,这儿介绍经历公式的算法:

模值=“二选大”+0.416ד二选小”

先对I路信号和Q路信号别离取绝对值,用比较器判别二者的巨细,取其间大的值给“二选大”,小的值给“二选小”,在程序中调用一次乘法器,和一次加法器即可核算出信号的模值。

为确保接收机的灵敏度,选用带门限的AGC电路(又称推迟式AGC电路),对输入信号与门限值之比取对数,即为输入信号与门限的差错,对数运算可运用CPLD器材的片内ROM用查表法完成。

积分器的功用是回忆前一采样周期的AGC操控码,并依据本次采样周期核算的差错值对其进行调整,最终使接收机的视频输出崎岖稳定在门限电平邻近,崎岖崎岖小于1dB。

3、 数控衰减器在中频电路中引进的冲击振动问题

因为AGC操控码的开关效果会在数控衰减器的输出端发生冲击振动,这种冲击振动是不行消除的,他会对中频信号形成搅扰,成为假方针,损坏接收机的正常作业。采纳以下办法可将这种冲击振动对接收机的影响降至最小。

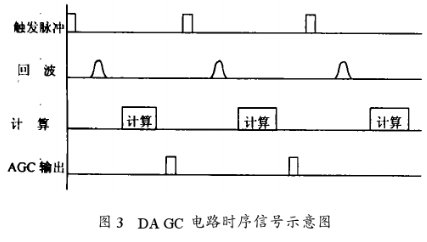

(1)合理设计时序电路

数控衰减器发生的冲击振动尽管不能彻底消除,但假如把AGC操控码的改变操控在雷达的休止期内,就会防止冲击振动搅扰中频信号。时序电路用以发生一切功用模块所需的同步信号,时序信号的波形图如图3所示。

(2)数控衰减器的推迟时刻有必要尽或许小,详细数值首要取决于雷达休止期的时刻。

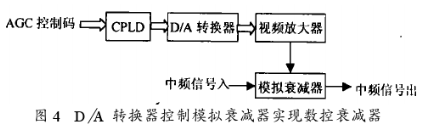

4、 数控衰减器的完成

数控衰减器的完成办法有2种:一种是用开关选I通电组网络完成,其缺陷是小衰减量位电路是失配的,I驻波比较大,高衰减量位的精度不易确保,组合起来I堆集差错较大。另一种是运用D/A转化器输出操控模仿衰减器完成数控衰减器,操控精度简单确保,功用图如图4所示。 模仿衰减器操控的线性度一般比较差,AGC操控码一般是8b,直接用这8b数据输入给D/A转化器去操控模仿衰减器,其操控精度是不能满意接收机的目标要求的,图4中的CPLD器材实际上是完成了EPROM的功用,EPROM的地址是AGC操控码,其数据输出能够挑选12b,选用12b的D/A转化器输出操控模仿衰减器,操控精度可到达0.5dB。假如这部分电路放在中放盒里,CPLD器材可挑选EPM7128SLC84-6,尽管该器材没有片内存储器,但用VerilogHDL言语编程很简单实~EPROM的功用,单片EPMTl28器材可代替4个8b的EPROM器材,完成电路的小型化。

5 、结 语

增益操控电路是雷达接收机的重要辅佐电路,前期的雷达选用模仿AGC电路,不便于调试,后来选用EPROM和D/A转化器对模仿衰减器的操控曲线加以批改,使接收机易于调试,但电路集成度低,设备量大。本文中介绍的数字增益操控电路用单片CPLD器材完成,电路参数调整灵敏方便,一起也完成了电路板的小型化。

责任编辑:gt