现在,嵌入式多核处理器已经在嵌入式设备范畴得到广泛运用,但嵌人式体系软件开发技能还停留在传统单核形式,并没有充分发挥多核处理器的功能。程序并行化优化现在在PC渠道上有必定运用,但在嵌入式渠道上还很少,别的,嵌入式多核处理器与PC渠道多核处理器有很大不同,因而不能直接将PC渠道的并行化优化办法应用到嵌人式渠道。本文分别从使命并行和缓存优化两方面进行并行化优化的研讨,探求在嵌人式多核处理器上对程序进行并行化优化的办法。

1 嵌入式多核处理器结构

嵌人式多核处理器的结构包含同构(Symmetric)和异构(Asymmetric)两种。同构是指内部核的结构是相同的,这种结构现在广泛应用在PC多核处理器;而异构是指内部核的结构是不同的,这种结构常常在嵌入式范畴运用,常见的是通用嵌入式处理器+DSP核。本文探求的嵌入式多核处理器选用同构结构,完成同一段代码在不同处理器上的并行履行。

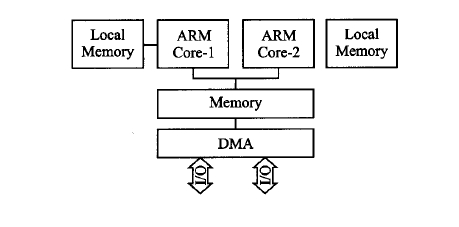

图1 ARM SMP处理器结构

在现在嵌入式范畴中,运用最为广泛的为ARM 处理器,因而以ARM 双核处理器OMAP4430作为研讨目标。ARM 对称多处理(Symmetric Multi-Processing,SMP)结构如图1所示,依据程序的局部性原理,每一个处理器都具有私有的内存(Local Memory),常见的是一级缓存(L1Cache)。但是,多个处理器之间又涉及到彼此通讯问题,因而在常见的ARM 处理器中运用二级缓存(L2 Cache)来处理这一问题。根据对称多处理器结构,一切的处理器(一般为2的倍数)在硬件结构上都是相同的,在运用体系资源上也是相等的。在嵌入式多核渠道上进行并行化优化,需求考虑以下问题:

① 并行化程序的功能取决于程序中串行化部分,程序功能不会跟着并行线程数目的提高而不断提高;

② 嵌入式多核处理器相对于PC处理器而言,其总线速度较慢,而且缓存(Cache)更小,会形成很多数据在内存(Memory)和缓存(Cache)问不断复制,因而在进行并行化优化的过程中,应考虑缓存友好性(Cache friendly);

③ 程序并行化履行线程数目应当小于或等于物理处理器的数目,线程过多会形成线程间抢占处理器资源,致使并行化功能下降。

2 OpenMP并行化优化

2.1 0penMP作业原理简介

OpenMP是一个根据同享内存形式的跨渠道多线程并行的编程接口。主线程生成一系列的子线程,并将使命映射到子线程进行履行,这些子线程并行履行,由运转时环境将线程分配给不同的物理处理器。默许情况下,各个线程独立履行并行区域的代码。能够运用work-sharingconstructs来区分使命,使每个线程履行其分配部分的代码。经过这种办法,运用OpenMP能够完成使命并行和数据并行。

图2 使命并行模型

使命并行形式创立一系列独立的线程,每一个线程运转一个使命,线程之间彼此独立,如图2所示。OpenMP运用编译原语session direcTIve和task direcTIve来完成使命分配,每个线程能够独立运转不同的代码区域,一起支撑使命的嵌套和递归。一旦创立使命,该使命就可能会在线程池(其巨细等于物理线程数目)中闲暇的线程上履行。

数据并行也便是数据级并行,对使命中处理的数据进行分块并行履行,如图3所示。C语言中的for循环最适合运用数据并行。