现在,对视频信号收集、记载和处理体系(视频收集卡、图画记载仪和电视盯梢体系等)的研讨测验现已非常广泛。在对这些体系进行测验的过程中,需求测验者供给契合该体系输入制式要求的视频信号。针对多种被测体系及被测方针,测验者应该供给不同品种和制式的视频信号。以往对这些体系进行测验时,人们常常运用探测器对靶板进行成像,将发生的视频信号送入被测体系。该测验办法给体系点评引进两方面的差错:一是靶板的制造差错,二是探测器自身的成像质量差错。针对这些差错,国内外逐渐运用可以供给模仿图画的视频信号发生器来替代传统的测验设备[1-3].现场可编程门阵列(FPGA)具有高集成度、高可靠性以及开发工具智能化等特色,现在逐渐成为杂乱数字电路规划的抱负首选[ 4].考虑到视频信号时序要求严厉以及硬件小型化的要求,选用FPGA来规划视频信号发生器,与其他规划办法比较,极大地缩短了开发周期,进步了测验精度。

1硬件完结

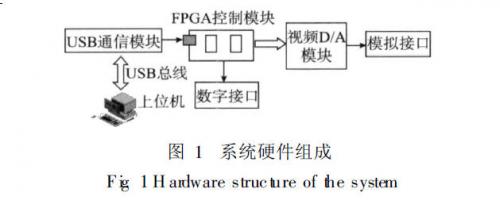

体系由USB通讯模块、FPGA操控模块、视频D/A模块和输出接口模块组成。硬件组成如图1所示。

1. 1作业原理

上位机经过USB总线与FPGA进行通讯,将模仿方针或靶板的信息以及其他操控信号传送给FPGA.FPGA对接纳到的数据进行判别和核算,最终输出具有时序联系的数字信号。假如体系需求输出模仿视频信号,那么将数字信号送入视频D/A转化电路,输出与被测体系制式相符的视频信号;假如被测体系接纳数字信号,那么将数字信号进行调度后,直接送入被测体系。

1. 2与上位机通讯办法的挑选

曾经咱们开发的视频信号发生器挑选了串口通讯的办法与上位机进行数据传输,该通讯办法具有开发简略,成本低的特色。可是在运用过程中发现了以下问题:一是不支持热插拔,接上视频信号发生器后,主机需求重新启动;二是需求为视频信号发生器独自供给电源;三是数据传输慢,不利于体系的扩展。

针对以上问题,决议选用USB通讯的办法。USB接口具有热插拔、传输速度快以及便携等特色[5] ,可以彻底满意本体系的规划要求。当本体系接入PC的USB接口时, PC将固件主动下载到USB接口芯片中,测验者只需求操作PC机上的使用程序界面,就可以完结相关的测验作业。此外, USB接口供给的+5V电源,它的电流可以到达几百mA,彻底可以驱动体系进行正常作业(软件仿真得到FPGA模块在生成某种视频信号时的功耗为100 mW左右),省去了体系供电电源的规划作业,这样缩小了体系体积,进步了体系的便携功用。

1. 3 FPGA操控模块FPGA操控模块是整个体系的中心。

以生成规范CCIR制式视频信号为例来介绍该模块的规划办法。依据CCIR制式的电视信号规范,它选用隔行扫描的办法,每场312.5行,行频15 625 Hz,场频50 H z,水平有用像素点768,笔直有用像素点575.因为选用了隔行扫描的办法,视频信号中就有必要包括前后均衡脉冲。再加上场同步中的开槽脉冲,这些脉冲信号的引进会进步输出视频图画的质量,因而模仿该类信号是该模块规划的要害。

因为CC IR制式视频信号归于模仿信号,所以FPGA输出的数据以及操控信号需求进入D /A转化电路。这儿选用了AD公司的3路10位视频D/A芯片,该芯片的输入端是复合同步信号、复合消隐信号、时钟信号、3路(R、G、B)图画数据信号以及其他操控信号,最终输出3路模仿视频信号。

因而, FPGA操控模块需求为视频D/A转化模块供给以上所需的输入信号。本文选用了模块化的规划办法,运用Verilog硬件描绘言语生成各种子模块,再将这些子模块进行顶层的衔接,最终输出图画数据及操控信号。模块的整体结构如图2所示。

在规划各子模块的过程中,充分运用了FPGA规划软件时序仿真的功用,这给调试以及选取最优模块带来极大的便利。图3是运用M odelSmi SE 6. 0软件仿真出的开槽脉冲、均衡脉冲、行同步、行消隐和场消隐子模块时序图。

图中, kcmc是开槽脉冲模块,其间高电平时刻是4.7μs,低电平时刻为27.3μs; jhmc代表前后均衡脉冲模块,高电平29.65μs,低电平2.35μs;hsyn代表了行同步脉冲模块,周期64μs,同步脉冲宽度4.7μs,前肩1.5μs,后肩5.8μs; hblnk是行消隐信号模块,消隐脉冲宽度12μs.在本体系中,运用FPGA的下载配备软件生成体系的配备文件(MCS格局),然后经JTAG口将配备文件下载到FPGA操控模块的PROM中。当体系每次加电后,PROM将其存储的文件配备到FPGA中, FPGA开端正常作业,完结相应的功用。针对这个特色,可以依据测验需求随时更新配备文件,完结不同品种被测体系的测验作业,使测验作业更具有灵活性。

1. 4视频D/A转化模块

将体系输出的规范和非规范模仿视频信号进行比较,发现它们有相似的当地,即都包括同步信号,并且对同步信号电平有特定的要求。规范视频信号中要求同步电平比消隐电平低0. 3 V,某型配备输出的非规范视频信号要求同步电平严厉操控在- 0. 3 V.同步电平的这些特性就要求规划者有必要合理挑选视频D /A转化芯片。

在本体系中选取了AD公司的三路10位视频D/A芯片。只要对该芯片的输入端(复合同步、消隐信号、时钟信号,数据信号等)进行编程,体系就可以输出不同制式的模仿视频信号。表1是本体系规划选用的视频输出真值表[6].

依据该真值表,运用FPGA严厉操控它们的时序联系,就可以发生多种制式的模仿视频信号,该办法增强了视频信号发生器的扩展性和通用性。视频D /A转化电路板及同轴电缆输出接口什物如图4所示。

2体系在电视盯梢功用检测中的使用研讨

2.1 电视盯梢功用方针和检测办法

电视盯梢箱是电视盯梢体系中完结盯梢和查找的要害部分。传统的电视盯梢箱盯梢功用测验选用的是室内标志法和机械靶标法等,这些测验办法中供给的模仿方针具有精度低和可控性差的缺陷[7].后来呈现了根据ISA总线的模仿方针卡,可是该卡运用时有必要插在PC的插槽上,一起该测验仪器的体积较大,并且扩展性欠好。

可以运用根据FPGA的视频信号发生器完结电视盯梢功用的检测。

最小盯梢方针、最小盯梢对比度、盯梢速度、方针捕获概率等是点评电视盯梢箱盯梢功用的重要方针[ 8].针对这些方针,要求本视频信号发生器输出的模仿方针,在速度、运动办法、对比度、视场中方位和巨细上具有可控的功用。

以最小盯梢方针测验来阐明该功用的完结办法。最小盯梢方针测验要求模仿方针是运动方针,测验过程中,测验者经过改动模仿方针的巨细来调查波门的盯梢或查找状况,然后判别出最小盯梢方针巨细。因而,需求在FPGA内部经过必定的算法来满意测验体系对模仿方针提出的要求。图5是本项测验中水平往复运动方针生成的算法流程图。

2.2 测验成果剖析运用

该视频信号发生器对某型电视盯梢体系电视盯梢箱进行盯梢功用测验,测验时将视频信号发生器与被测电视盯梢箱衔接,然后设定被测配备的某些作业参数,最终获得了该配备的部分盯梢功用参数。测验成果如表2所示。从盯梢功用测验成果中可以看出,最小盯梢方针在3 @ 3~ 4 @ 4像素之间,最小盯梢对比度在3% ~ 4%之间,水平最大盯梢速度在4. 22~ 4. 24视场/秒之间,捕获概率一直为100% ,它们的改变起伏一直都操控在规划要求的范围内。

一起,运用一台标定后的某型电视盯梢检测仪对被测电视盯梢箱进行测验,得到的测验成果根本与表2中的相吻合,然后验证了本视频信号发生器的作业可靠性。

图6和图7是在测验前将本视频信号发生器接入某图画收集卡获取的模仿方针图画。

3定论

根据FPGA的视频信号发生器可以满意多种被测视频输入体系对视频信号制式的要求。它选用USB技能完结与上位机的通讯,处理了作业电源的问题,进步了该体系的通用性和扩展性。将该视频信号发生器使用在某型电视盯梢体系电视盯梢箱的盯梢功用测验中,获得了该配备的部分电视盯梢功用参数,经过剖析试验数据,证明了该体系具有测验精度高、作业稳定性好的特色。可以说该视频信号发生器可以为精确点评配备的战斗功用供给必要的技能保证。往后,可以对该体系进行扩展,将它使用在更多的测验领域中,所以其使用远景非常广泛。