存储深度(Record Length)也称记载长度,它标明示波器能够保存的采样点的个数。存储深度假如为“20000个采样点”则一般在技能目标中会写作“2Mpts”(这儿的pts能够理解为“points”的缩写)或2MS(这儿的S也能够理解为“samples”的意思)。

存储深度表现在物理介质上其实是某种存储器的容量,存储器容量的巨细也便是存储深度。示波器收集的样点存入到存储器里边,当存储器保存满了,老的采样点会主动溢出,示波器不断采样得到的新的采样点又会填充进来,就这样循环往复,直到示波器被触发信号“叫停”,每“叫停”一次,示波器就将存储器中保存的这些采样点“搬移”到示波器的屏幕上进行显现,这两次“搬移”之间等候的时刻被称为“死区时刻”。有个形象的比方,存储器就像一个“水缸”,“水缸”的容量便是“存储深度“,假如运用一个“水龙头”以稳定的速度对水缸灌水,水龙头的水流速便是“采样率”,当水缸现已被注满水后,水龙头仍然在对水缸灌水,这时候水缸里的水有一部分就会溢出来,但水缸的全体容量是坚持不变的。

存储深度=采样率 × 采样时刻,关于数字示波器,其最大存储深度是必定的,可是在实践测验中所运用的存储长度却是可变的。 在存储深度必定的状况下,存储速度越快,存储时刻就越短,他们之间是一个反比联系。一起采样率跟时基(timebase)是一个联动的联系,也便是调理时基档位越小采样率越高。存储速度等效于采样率,存储时刻等效于采样时刻,采样时刻由示波器的显现窗口所代表的时刻决议。比如其时基挑选10μs/div,因为水平轴是10格(有些示波器是12格或14格),因而采样时刻为100μs,在1Mpts的存储深度下,当时的实践采样率为1M÷100μs =10 GS/s , 假如存储深度只需250Kpts,那当时的实践采样率就只需2.5GS/s了。

某些厂商制作的示波器,当时的最大存储深度能够在菜单中设置。一旦设置好当时的最大存储深度之后,调理水平常基,跟着采样时刻的添加,示波器的存储深度会主动添加,这个进程中采样率坚持不变;存储深度随采样时刻添加到当时设置的最大存储深度后,假如持续添加采样时刻,采样率会主动下降,存储深度坚持不变。可是在有些状况下,因为采样率和采样时刻的步进是在固定的若干个档位下跳变,并不是接连细调的,两者相乘不必定和最大存储深度的数值相同,这时候示波器或许会主动调整当时的采样率或存储深度,使得它们三者满意乘积联系。

由存储联系式知道:进步示波器的存储深度能够直接进步示波器的采样率,当要丈量较长时刻的波形时,因为存储深度是固定的,所以只能下降采样率来到达,但这样必然形成波形质量的下降;假如增大存储深度,则能够以更高的采样率来丈量,以获取不失真的波形。

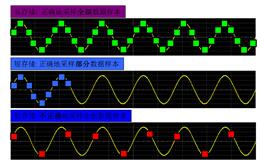

下图中第一个图形标明在采样率满足的前提下,调查多个周期的样本,需求的存储深度很长,图示中需求36个采样点。第二个图形采样率仍然坚持便利,但存储深度变小,只需9个采样点,因而只能采样一个周期多点的波形。第三个波形仍然是存储深度很小,只需9个采样点,但仍然要采样和第一个图形相同多个周期的波形,其结果是采样率变小,丈量得到的波形就会失真。

关于高端示波器,存储器芯片一直是核心技能,示波器中的ADC速率太快,一般的存储介质底子来不及在这么短的时刻内“吞吐”那么大的数据量。比如ADC的采样速率是20GS/s,也便是说每秒要收集20G个点,而每个点是由8个0和1组成,假如ADC的输出是彻底依照串行数据传送到存储器中,那么传输速率便是160Gbps,现在的PCI-Express 3.0的速率是8 Gbps,最高速的高速芯片在单板上传输的速率是25 Gbps,但还不老练,也没用到示波器上,高速的ADC采样点怎样传输到存储器中,这是一个难题。其实,这么高速的ADC也不或许是单芯片规划的,内部是由许多的2.5GS/s或1.25S/s、250MS/s的小的ADC交错拼接的。

跟着示波器技能的开展,现在存在两种架构形式,一种是根据PC渠道的,别的一种是嵌入式的,主要是根据FPGA完成的。跟着DDR内存速率的进步和FPGA核算才干的增强,现在根据FPGA核算渠道的存储器芯片现已不再奥秘,多是选用工业上的DDR内存颗粒了,因而存储深度这个目标在不顾及存储的采样点是否实在的被显现、被剖析的状况下,能够做的特别大了。但往往实在状况是,尽管存储深度很高,但显现的采样点数和剖析的采样点数或许只需千分之几,在这类产品中,屏幕上看到的波形对应的存储深度并不等于采样率乘以采样时刻。

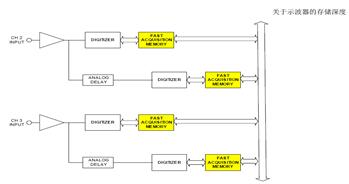

示波器多个通道一起作业时,采样率和存储深度能够作业在叠加形式。大都示波器是2个通道叠加,也有的是4个通道叠加。下图标明的是两个通道叠加运用的作业原理示意图:

通道1和通道2替换采样,一个通道推迟1/2的采样周期使得采样率加倍,示波器在采样进程中替换读取存储器中的采样点,全体存储深度也相应加倍。因而,为了取得最大的采样率和存储深度,在只运用两个通道进行丈量时,关于两两叠加的形式,主张只翻开1、2通道中的一个,3、4通道中的一个。

现代示波器的存储深度尽管很高,动辄捕获不计其数个数据样本,可是示波器的显现屏在水平方向上的图象分辨率往往只需1280个乃至更少的像素。示波器如何将那么多的点挤在这么小的屏幕上显现出来呢?显现的紧缩算法处理了这个问题。紧缩算法将捕获的许多数据样本分红许多小段,每一段只抽取最大值和最大值的数据点显现在屏幕上。这种紧缩算法在显现上加剧了信号的峰峰值在视觉上的效应,表现为波形看起来比打开之后的部分扩大的没有被紧缩的波形有更多的噪声,波形轨道显得更粗。可是,也有些示波器即便选用了显现紧缩算法,但屏幕上显现的存储深度并不等于当时的采样率乘以采样时刻。屏幕上显现的仅仅部分波形,对应的是“采样时刻”的一部分,还有一部分“采样时刻”在屏幕的“外部”,需求旋转示波器面板上的“position”键,将屏幕外面收集的波形“移动”到屏幕显现的窗口。

有些低频信号中有高频噪声,有些高速信号中包含了低频调制,有些信号的改变进程十分缓慢,有些剖析自身只需样本数满足多才有意义,这四种状况下都需求长存储。前两种状况都需求将感兴趣的低频成分完好的捕获下来才干进行有意义的剖析。在许多的实践使用中都归于上述四种长存储的使用领域,例如电源软启动进程的丈量、电源纹波和电源噪声的丈量、FFT剖析、扩频时钟剖析、发现随机或稀有的过错等等。