摘要:文中根据对微处理器S3C2440A的显现操控模块和高性能视频D/A芯片ADV7120的研讨,提出了一种便携式视频展现台的规划计划。本计划选用130万像素的OV9650摄像头收集什物、文档、图片或许进程的图画数据,运用S3C2440自带的LCD操控器来发生契合VGA显现要求的时序逻辑,ADV7120将数字RGB信号转化成VGA显现需求的模仿五颜六色信号。经过TFT—LCD扫描显现的时序与VGA扫描显现时序的匹配来驱动VGA显现。测验结果表明,计划切实可行,到达正常显现颜色信息的要求。

要害词:便携式视频展现台;嵌入式linux;LCD操控器;ADV7120;VGA时序

视频展现台是将什物、文稿、图片和进程等信息转化为图画信号输出在投影机、显现器上展现出来的一种演示设备。便携式视频展现台因为具有体积小,易于带着等长处,被广泛用于教育、大型会议及产品展现等场合,具有较大的研讨远景。本视频展现台的规划选用三星根据ARM9内核的S3C2440A芯片,运用模块化的规划准则;具有体积小、便带着、低功耗、易维护性等特色,整个体系的规划由两部分构成,分别是什物、图片、文档或许进程等图画收集部分和VGA传输显现部分。此视频展现台的显现分辨率为800×600。

1 视频展现台体系结构规划

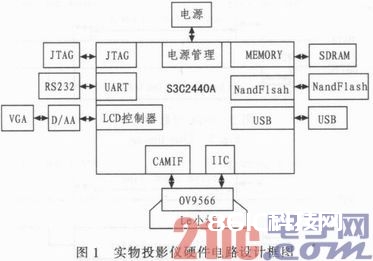

本便携式视频展现台选用三星S3C2440A处理器,其CPU的作业频率可达400 MHz,能够很好的处理图画数据。它的外设包含:LCD操控器、CAMIF单元、UART接口、IICBUS接口、USB主从接口等。体系选用具有极快读写速度的2片32 MB的SDRAM来确保linux操作体系的流通运转,选用具有掉电维护功用的128 MB的Nancmash来寄存操作体系和驱动程序。此外,130万像素的ov9650摄像头用来收集视频图画数据,ADV 7120将数字RGB信号转化成VGA显现需求的模仿五颜六色信号,显现分辨率为800×600。电源办理模块能够供给多种供电,包含芯片内核电压选用1.8 V供电,芯片的IO口部分选用3.3 V供电。为了给什物、文档、图片或许演示进程供给照明光源,在ov9650摄像头周围加了一圈led小灯。下图1是计划的硬件电路规划框图。

2 视频图画收集模块

2.1 视频收集硬件接口及其剖析

视频收集模块是本便携式视频展现台的一个重要组块之一。本模块选用摄像头接口操控单元CAMIF和IIC总线来操控和传输OV9650摄像头收集什物、图片、文档或许进程等视频数据。挑选CMOS传感器是因为它有功耗低、编程便利、本钱低一级长处。其主要引脚及功用描绘如下:CAMCLKOUT是CPU输出的采样时钟,帧同步信号VSYNC、行同步信号HREF、像素时钟信号PCLK由OV9650内部发生,输入到S3C2440A芯片中,用于对图画收集进行操控。摄像头在每个PCLK脉冲进程中顺次收集一个字节的数据,直到一帧图画数据收集完结。

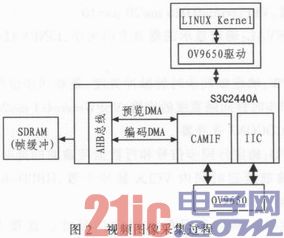

摄像头收集的数据经过处理后进入帧缓冲区,帧缓冲区由4个Ping Pong存贮器组成,因而图画帧的读写操作能够一起进行。然后经过预览DMA连到AHB总线上,经过AHB总线将数据送往内存。整个进程由linux操作体系来操控,如图2所示。

2.2 视频收集驱动规划

file_operations结构是Linux2.6内核供给的一个规范化的文件操作完成接口。界说ov9650_ops为file_operations结构。编写用于上层软件接口函数:

struct file_operations ov9650_ops=

{

open:ov9650_open,

release:ov9650_release,

read:ov9650_read,

write:ov9650_write,

iocfl:ov9650_ioctl,

};

经过这些调用函数,应用程序就可完成对CMOS摄像头的翻开、封闭、视频数据的读取、内部寄存器的设置等进行操作。在发动驱动程序时,体系首要调用现已界说的ov9650摄像头驱动程序的进口函数init(ov9650_init)对摄像头进行初始化,初始化的主要内容是复位、经过I%&&&&&%装备相关摄像头寄存器、摄像头采样时钟装备以及中止装备等,然后等候进一步指令。应用程序运用完毕后,体系调用现已界说的ov9650出口函数exit(ov9650_exit)退出。

3 VGA显现模块

3.1 LCD操控器接口和VGA接口描绘

本便携式视频展现台的另一个重要组块是VGA显现模块。S3C2440A带有LCD操控器,能够很便利地操控驱动扫描式接口的TFT显现。其主要功用引脚有:像素时钟信号引脚VCLK/LCD,场同步信号引脚VFRAME/VSYNC,行同步信号引脚VLINE/HSYNC,VD[23:0]是LCD数据输出端口。当把VSYNC、HSYNC、VCLOCK等信号参数设定好,并把帧内存(frame memory)的地址告知LCD操控器后,LCD操控器即可经过DMA主动获取帧内存中的图画数据。

VGA接口运用模仿RGB通道,逐点、逐行扫描。VGA接口信号为模仿信号,其要害信号有5个,分别是行同步信号,场同步信号,赤色模仿信号,绿色模仿信号和篮色模仿信号。电子枪从左至右,从上而下的进行扫描,每行完毕时,用行同步信号进行同步。扫描完一切的行后用场同步信号进行场同步。

经过比较LCD扫描式接口时序和VGA时序可知,LCD操控器驱动TFT显现的行场同步信号时序和VGA行场同步信号时序很像。仅仅信号的极性VGA是负极性,LCD信号是正极性,这个经过调整Linux内核显现模块来调整LCD的时序以习惯SVGA时序即可。因而,能够运用高性能视频D/A转化芯片ADV7120将S3C2440A自带的LCD扫描式接口转化为VGA接口,然后用带有VGA接口的显现器显现。此外,LCD操控器用于操控数据信号的使能的引脚VDEN在D/A转化模块中可用来操控信号转化的使能,LCD操控器的VCLK可用作D/A转化模块的时钟信号。

3.2 高性能视频D/A转化芯片ADV7120

ADV7120的输入及操控信号十分简略:3组8位的数字视频数据输入端,用以衔接LCD操控器的数据输出接口VD[23:0],数据输入端选用规范TTL电平接口;4条视频操控信号线包含复合同步信号SYNC、消隐信号BLANK、白电平参阅信号REF WHITE和像素时钟信号CLOCK,外接一个123V数模转化参阅电压源和1个输出满度调理。

ADV7120的输出信号只要4条:3条模仿RGB信号和同步参阅电流输出信号Isync。VGA接口的行场同步信号和LCD扫描式接口的行场同步信号是共同的,因而LCD操控器接口中的行场同步扫描信号HSYNC和VSYNC直接接到VGA接口。LCD操控器和VGA接口是由硬件完成的两种接口的电器转接,不需求写任何驱动程序,这是在嵌入式体系平台上扩张VGA接口最便利的计划,也是本便携式视频展现台体积小,易带着性规划的根底。