从开端学FPGA到现在大略算来的话,现已有3个多月了,就现在而言,我并不确认自己是不是高手们所说的入门了。可是不论现在的水平怎么,今日就总结一下自己学习它的感受或一些知道吧。

首要,先说一下自己的在学习中所发现自己的缺乏之处:

1. 不会总结。

2. 学习的良好习惯没养成。

在写FPGA的根本模块时,遇到的问题有许多,比如,写代码时的正告,特别是一些不能忽视的正告,每次遇届时,总是还要查看一瞬间才干改过来,或许有的正告现已呈现了几回,可是便是处理不掉。每次在学一个模块时,只需是看懂了,它的一些要点就没有及时的记载在簿本上,只需单个的想起来时,才会做笔记。每做完一个模块,没有及时记载下自己从这个模块中学到了什么。上面的缺乏,都是在写模块的进程中,自己逐步露出出来的。我很幸亏自己的一些问题能及时的被发现,尽管年前的学习将暂告一段落,可是,在年后的学习中,我必定会时间记住自己曾经在学习上呈现了怎样的缺乏,防止相似的作业再次发生。像遇到正告时,都要记载下来,经过改正后,要注释,写下正告的原因,定时看一下。我前次写的一个代码就没有注释现在自己都看不懂了http://www.51hei.com/mcu/967.html ,每次写模块的时分,都要记下要点常识,即使是自己懂得的,好记忆都是比不过烂笔头的。

其次,就谈一下自己在学习FPGA中,截止现在,学到了什么,知道到那些。

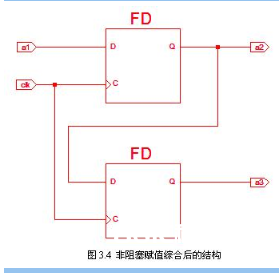

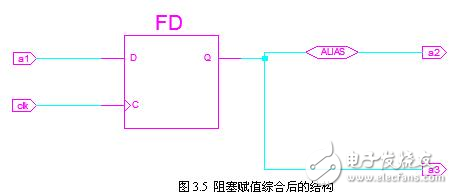

FPGA简略的说,便是现场可编程逻辑阵列。它的内部是逻辑单元,它们之间能够用线衔接,至于以怎样的方式相连,则能够依据使用者写入的逻辑决议。每次布线都会重新组合逻辑单元,然后能够恣意的编写不同的逻辑。当然,条件是界说的逻辑块不超出它可读写的最大值。或许自己说的术语并不专业,又或许是了解或表达的不透彻,但随着学习的加深,必定会有愈加透彻的了解吧。学习FPGA ,尽管材料许多,可是看的材料并不是许多,除了看夏宇闻编写的语法书外,看的最多的便是特权同学的,一个年青的电子工程师,他便是经过自己的尽力和持之以恒有了现在的水平,尽管不能说是最好的工程师,可是,他在这条路上的生长进程,却代表着更广阔的青年的斗争轨道。他的《浅显易懂玩转FPGA》这本书,曾经只听网友说不错,比及自己开端看后,发现里边的内容确实是值得学习,不只是学习的层次性,一同里边的办法也是很不错的。经过看书和做模块,自己对FPGA中的几个学习要点或许说菜鸟有必要清楚了解的常识,有了一些自己的观点,首要是堵塞与非堵塞赋值的差异,堵塞赋值是只需你给一个寄存器赋值了,它在此句子完毕后,其值立马就改动,而非堵塞赋值却不同,赋值后,寄存器存储的值并没有改动,仍是前次所赋得值,只需当此进程块完毕后,下一次脉冲来时,输出才会改动,确切的说,某些情况下,能够将堵塞赋值了解为移位寄存器。它们的不同之处能够有下图看出:

图一:非堵塞赋值

图二:堵塞赋值

当想把a先赋给b,然后赋给c时,堵塞赋值是b和c在同一个脉冲下,一同等于a,而非堵塞赋值则是先把a赋给b,鄙人一个脉冲时,再将b赋给c,这才契合规划的初衷。所以,在运用时,要注意到它们的不同之处。在时序逻辑中,用非堵塞赋值,而在组合逻辑顶用堵塞赋值。

除了堵塞与非堵塞赋值的差异要了解清楚外,状况机又是一个要点,会运用状况机十分重要,这是在写可调时钟时,自己深入认识到的,其时写可调时钟时,想要调理它的不同形式,可是又不能在不同的进程块中,对同一个变量赋值(和C51的不同之处),所以,其时写此代码的时分,走了弯路。这几回写的几个代码中也用到了状况机,如:矩阵键盘的扫描,串入并出和并入串出,AD0832。它让我越来越感觉到,要想操控好一个层次分明的作业流程,状况机不行少。而要想写好一个状况机,首要要做的便是要确认若干个状况,清晰各个状况之间的逻辑关系,搬运条件等等。尽管,到现在为止,自己还有几个模块没写完,可是,自己对状况机现已不再是不知道怎样用,而变为遇到一个问题时,总是想到状况机是否能处理这个问题。我想这也是自己在这方面踏出的第一步吧。除了这两点外,让我感受很大的便是除法器的编写,曾经在单片机中,用到除法,只需求一个符号:“/”就能搞定,可是,现在让自己写一个除法器,要弄懂它的原理,这让我认识到,往往看起来很简略的一件事,在其背面,总有许多需求咱们去发掘或许说是去知道和学习的当地。除此之外,我感觉有几种编程技巧挺不错的,例如:“Wire keysign=cnt[19]”这种置标志位的办法,只需当位宽为19的寄存器“cnt”计数计满时,keysign才变为1,一同只保存一个周期,而寄存器“cnt”计满后,主动清零,当下次计满时,keysign才再次被赋值为1;这在矩阵键盘的扫描中,是十分重要的。还有便是移位寄存器的使用,包含位拼接等等,都挺经典的。

在学习的进程中,经过学习到的这几种相对较好的编程办法后,我也认识到了自己在学习中的一些不正确的思维,如:曾经总感觉既然是写代码的,最好仍是自己写,这样才比较好,照着他人写好的代码看,感觉如同少点什么似的,这或许是心理作用在做怪,而这几回模块写下来,自己体悟挺深的,刚开端总是自己想着写,进展不只慢,功率也不是很高。这让我抑郁不已,后来看他人都是看着他人的代码改写的,我想了挺多的。看他人的代码,能看懂其实也是一种本事,作为初级者,首要便是一个学习的进程,不或许什么东西都是“自来熟”,只需先学习他人的利益,把握了必定的根底,才干去立异。这一点,在我看了网上一些人写的代码后愈加信任:大多数的根本模块代码,我们的编程思路都是十分相同。只需在编写一些大型的代码时,才会在原有的根底上去进行改善和交融。而这些技术离不开平常的堆集。

关于以上的总结,我信任在今后的学习中必定会对自己有极大的协助,它会时间警醒自己,在曾经的学习中,自己有哪些缺乏,今后千万不能再去犯相同的过错,不断地纠正,不断地前进,信任自己必定会学好FPGA的。