1、导言

在FPGA的开发运用中,大多数EDA软件(后边以altera QuartursII为例)都供给乘除法、开方运算的规划导游,或供给LPM宏函数,但遍及占用资源量大。而在许多信号处理运用中,要求核算精度高、资源灵敏而核算时延要求并不高,这时咱们需求一种确保核算正确且资源开支最低的FPGA完成方法,本文给出了完成乘除法、开方运算的FPGA串行完成算法,并与LPM宏函数进行了性价比比较。成果表明,本文给出的各算法核算精确,资源量远小于调用LPM宏函数。

2、算法描绘

2.1、乘法

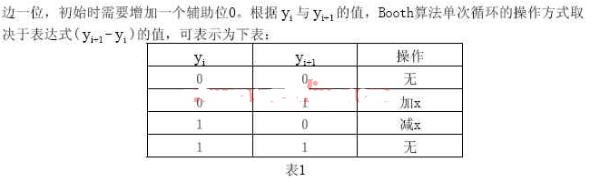

向左移位操作,那么乘积右移一位,相对而言能够以为乘数被扩大两倍。可见Booth算法只选用加法、减法和右移操作便可核算补码数据的乘积。对乘数从低位开端判别,依据两个数据位的状况决议进行加法或减法运算,每次将乘积项向右移一位。

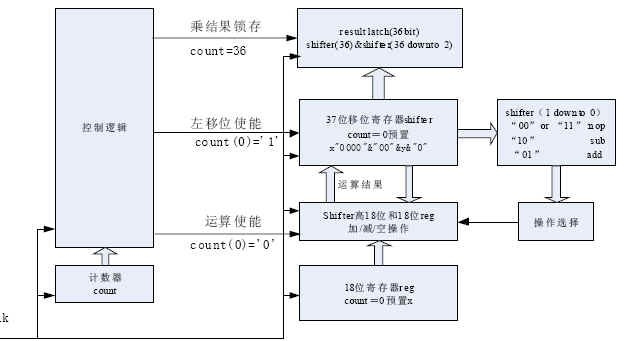

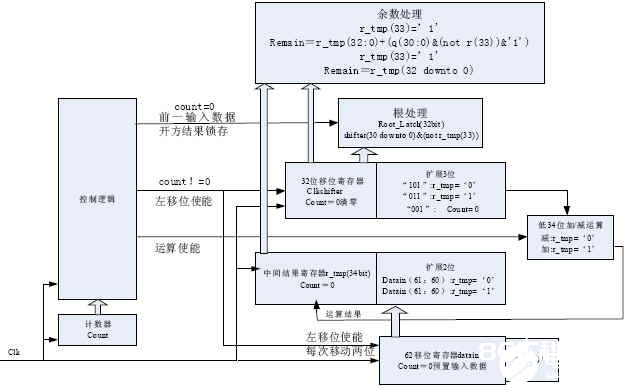

图1

完成结构如图1。可见,本算法将乘法转化为串行的加减和移位运算,然后节省了很多逻辑资源。

2.2、除法

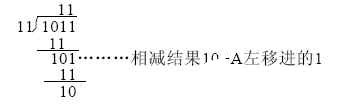

除法核算咱们选用经典的核算的方法,这种算法的完成思路清晰,完成的结构也很简略。咱们首要介绍原码除法的完成。

设:A、B均为无符号数,A=1011,B=0011,求A/B。其核算如下图:

图2

其特色可归纳如下:

(1)、 每次比较余数(被除数)和除数的巨细,确认商为1仍是0;

(2)、 每做一次减法,坚持余数不动,低位由被除数低位补进,再减去右移后的除数。

关于补码除法运算,为了简化中心判别进程,咱们能够先将除数和被除数取模,然后依照原码的核算方法求出商和余数,再依据除数和被除数的符号对核算成果进行批改即可。由此可见,有符号除法包括了无符号除法的运算进程,所以咱们这儿也侧重介绍有符号除法的核算进程。设:被除数(x)为56位,除数(y)为28位,考虑一切可能性,则商(q)取56位,余数(r)取28位。详细完成过程如下:

(1)、56位余数移位寄存器shx=mod(x),28位余数寄存器reg=mod(y),被除数符号flagx=sign(x),除数符号flagy=sign(y), 29位余数移位寄存器shr=0,56位余数移位寄存器shq=0,k=112;

(2)、 若k为奇数, shr左移一位低位补shx最高位, shx左移一位低位补0;

若k为偶数,则 if shrelse shq左移一位低位补1,shr=shr-reg;

(3)、 重复过程2,直到 ;

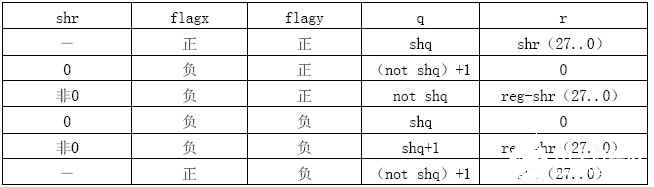

(4)、 成果批改(如表2)。

阐明:最终需求依据A、D的符号和shQ、shR、regD的值对核算成果进行批改。批改方法如下表。

表2

本算法因为依据经典方法完成,思路清晰,一起全串行操作也很大程度上降低了资源量。

2.3、开方

非冗余算法是经典的开方算法,其依据如下核算:

图3

3、FPGA完成

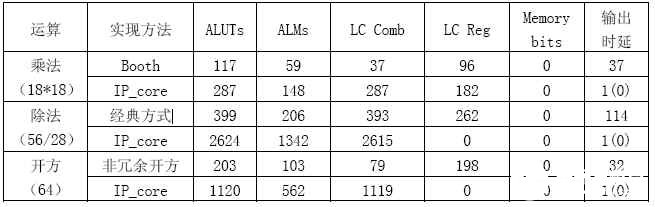

咱们在Altera公司的QuartusⅡ5.1软件环境下运用VHDL言语完成了上述各算法,并在StratixⅡEP2S30484C5芯片中完成。下面给出了各算法的资源耗费状况,并与IP_core作了比较(如表3)。

表3

能够看出本文中提出的算法对二进制数的乘除法以及开方占用资源很少,并且确保了核算精度;IP_core所用时刻最短(输出时延可调),但占用逻辑单元跟着位宽的添加急剧上升。由

此可见,当实践规划对逻辑单元运用要求不严苛时,便能够运用IP_core,其规划简略且核算时

延小。若对逻辑单元运用有要求且对核算时延不灵敏时,运用串行乘除法和开方是很好的挑选。

4、结束语

本文给出了乘除法、开方运算的FPGA串行完成算法,与IP_core方法比较,本文中的算法占用逻辑单元少,但核算周期较长,实践运用中能够考虑选用流水线等改善方法,以进一步缩短核算周期。

责任编辑:gt