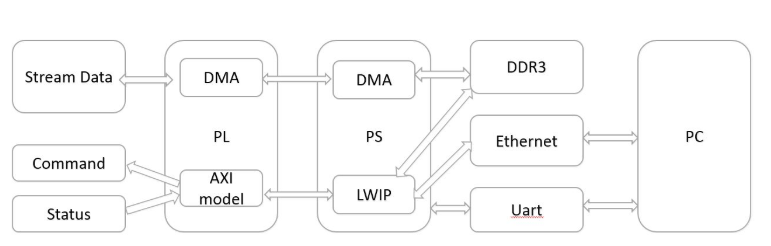

在探索了一段时间的Zynq后,自己制作了一块XC7Z020板子,板子到手后考虑运用中的整体结构。根本确认运用Ethernet为PC和board之间的通讯方法,DDR3作为PL端的大数据存储单元,而且划出一些寄存器用于PS和PL间的指令下达和状况回来用处。PL大数据传输例化DMA_IP core,衔接DDR3。

编写带AXI_lite接口的自定义IP_Core恣意读存DDR3,统筹PL扩展IO用处。在Ethernet运用中,PS SDK编写运用LWIP协议,并敞开UART接口便利调试。

根本结构如下:

Firmware 编写思路:

1. 在Vivado中编写用户自定义function_IP with AXI_lite;

2. 在Vivado中想调用ZYNQ7 processing system,AXI_DMA模块,并做相关设置;

3. 调用用户自定义funcTIon_IP with AXI_lite 模块;

4. 主动连线,并手动衔接必要信号;

5. 导出到SDK工程后,开端PL SDK编写,预备运用裸奔程序;

6. 其主要思路为初始化-等候-指令-履行-反应-等候,是和PC互动进程;

7. 上位机编写待续;