1 导言

跟着无线通信技能的小断开展,系统要求更高的集成度,更强的功用以及更低的功耗。一起,CMOS技能现已开展到深亚微米水平,使得CMOS器材的高频特性得到进一步改进,现已能与锗硅和砷化钾器材相媲美。别的,CMOS器材在功耗上占有优势,因而深亚微米的CMOS技能在无线通信系统中很有使用潜力。在射频接收机中,低噪声扩大器(LNA)占有重要方位,他在扩大输入的弱小信号的一起按捺随同的噪声。因而,低噪声系数与高增益是LNA的两个重要目标,当然这两个目标还要与功耗、线性度、输入输出匹配及小作业电流时的无条件稳定性彼此折衷。

常见的CMOS低噪声扩大器有差分输入(superhete-rodyne)、共栅(common-gate)、共源共栅(cascode)三种结构。差分LNA具有低噪声系数(NF)和有用按捺共模搅扰的特色,但关于相同的噪声系数,差分扩大器的功耗是单端扩大器的两倍,而且所占芯片面积较大;共栅扩大器输入阻抗匹配简单完成,具有较好的反相隔离度和稳定性,但噪声系数较大;共源共栅扩大器能够供给一个较高的增益和反相隔离度,但其增益和噪声系数遭到共源级的漏级衬底寄生效应的严重影响。

本文针对无线通信中蓝牙技能的重要频段,选用深亚微米技能TSMC 0.18μm CMOS工艺,规划了一种2.4 G的低噪声扩大器,并给出了ADS软件的仿真成果和评论。

2 电路规划

关于CMOS LNA来说,一般要求S21在10~20 dB间。假如增益太小,LNA不能将弱小的输入信号(-140~-40 dB,或0.03μV~3 mV)扩大到预订的值;假如增益太大,LNA又会影响下一级混频器的线性度。一般情况下,S11/S22应小于-10 dB,S12应满意小(《-20 dB)。此外,在输入输出端应进行阻抗匹配以进步功率增益。

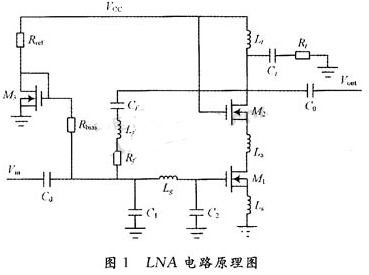

本文选用的LNA电路结构如图1所示。LNA的偏置电路由Rref,M3及Rbias组成。晶体管M3与M1构成一个电流镜,而且他的宽度是M1宽度的几分之一,以使偏置电路的附加功耗减到最少。经过M3的电流由电源电压和Rref以及M3的Vgs决议。电阻Rbias的值(20 kΩ)满意大以使他的等效噪声电流小到足以被疏忽。

关于输入端,Cd是一个隔直流的电容,Ls为源级负反应电感。C1,Lg和C2组成一个π型网络。因为高的品质因数会导致芯片面积添加,而太低的品质因数会使电感损耗添加并使噪声系数NF变坏,选用π型网络匹配能够较好地处理以上对立。在π型网络中,首要挑选一个具有高品质因数、便于集成的电感Lg,其次核算C1,C2使其满意输入匹配要求。

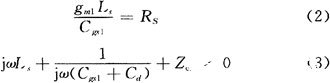

疏忽反应支路Lf,Cf与Rf以及偏置电路的影响,LNA的输入阻抗为:

![]()

其间,Cgs1为M1的栅-源复盖电容;Zeff为π型网络的等效阻抗;gm1为M1在饱满区的跨导;ω为中心频率。

当输入阻抗与电压源阻抗Rs匹配时,应有:

关于共栅级M2,其输入阻抗为:

![]()

一般情况下M1与M2之间并无匹配,但因为共源级的输出阻抗与共栅级的输入阻抗都是容性,因而在两级间添加一个电感La匹配以进步增益。

关于输出端,C0是一个隔直流的电容;Lt,Ct与Rt构成输出匹配网络,与下一级电路匹配。

图1中Lf,cf与Rf构成电压并联负反应。为了补偿高频增益,有必要使高频时的负反应量削减,因而,并联反应网络有必要是理性而不能是容性的。电容Cf是隔直流电容,其容量满意大,在作业频带内可看过短路。因为共源共栅的输出阻抗很大,因而Rf的取值下限为900~1 100Ω,以便能在不添加噪声系数的前提下进步电路带宽。在反应电阻Rf确认之后,应使Lf在欲提高的频率处的阻抗值ωLf挨近Rf值,大致按ωLf=(0.2~5)Rf选取,使反应阻抗随频率改变较大,反应量改变大,频率特性改变显着。

关于LNA而言,噪声首要来源于闪耀噪声、热噪声和散粒噪声。其间,闪耀噪声又称为1/f噪声,首要来源于场效应管的氧化膜与硅触摸面的工艺缺点或其他原因,一般在射频下疏忽不计。热噪声是因为电子热运动引起的,在射频情况下其量值将随频率的升高而显着增大。散粒噪声的巨细正比于作业电流。因而,低噪声扩大器首要考虑热噪声与散粒噪声的影响。

在有功耗束缚情况下到达最小噪声系数时的信号源品质因数Qs为:

![]()

当QsP确认后,最优化器材宽度为:

![]()

关于宽度为Wopt,P的器材,可得功耗束缚范围内的噪声系数:

![]()

把f0=2.4 GHz,Rs=50Ω,L=0.18 μm代入式(6)可得最小噪声系数时的沟道宽度大约为289 μm。因为最小噪声系数时的沟道宽度与最大增益时的沟道宽度并不共同,因而应挑选适宜的沟道宽度在最小噪声系数与最大增益之间折衷。

3 软件仿真

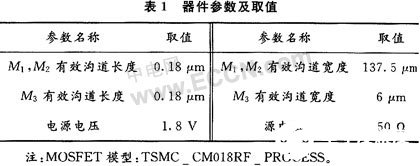

本文运用TSMC 0.18 μm CMOS工艺库,选用Agi-lent公司的ADS进行仿真,电路器材参数及取值如表1所示。

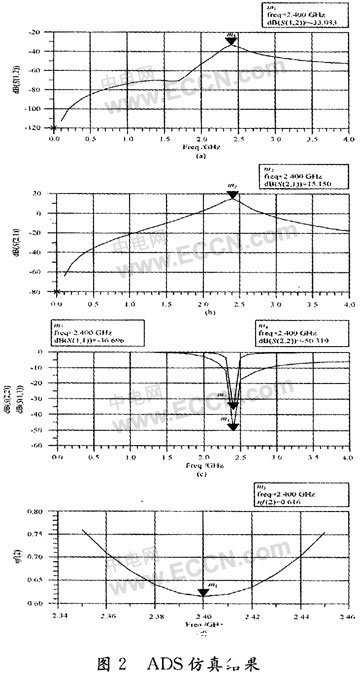

仿真如图2所示,在中心频率为2.4 G时,电路功率增益S21为15.15 dB,隔离度S12为-33.03 dB,输入与输出反射系数分别为-36.70 dB与-50.32 dB,噪声系数仅为0.62 dB。1.8 V时直流功耗为7.9 mW。这些目标能很好地满意RF电路对低噪声扩大器的规划要求。

4 结 语

从仿真成果能够看出,在共源共栅结构的基础上一起选用级间匹配、π型网络以及电压并联负反应的低噪声扩大器输入输出匹配杰出,这反映在电路的噪声系数到达了很好的水平,增益比不选用级间匹配和电压并联负反应时添加了约2 dB左右,到达规划要求。

选用此结构规划的深亚微米CMOS射频低噪声扩大器,因为规划中充分考虑了功耗、增益、噪声系数、线性度及品质因数之间的折衷联系,所以到达的规划功能优秀。在深亚微米水平上完成低噪声扩大器的规划具有重要意义,在大规模数模混合集成电路中很有使用潜力。

责任编辑:gt