1概述

MICRF500是用于ISM(工业、科学和医药)和SRDC(短距离设备)的专用发射和接纳芯片,其频率规模为700MHz~1GHz,选用FSK(频移键控)调制时的数据速率达128 kbauds,RF输出功率为10dBm,灵敏度为-104dBm,接纳形式电流耗费为12mA,发射形式电流耗费为50mA,低功耗形式电流耗费 2μA。可广泛运用于遥测、无线操控、无线数据中继、无线操控体系、无线调制解调器和无线安全等体系中。

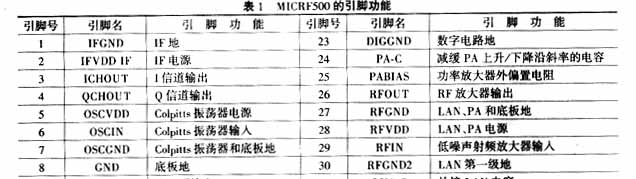

2芯片封装与引脚功用

MICRF500选用44-LQFP(BLQ)封装,各引脚功用如表1所列。

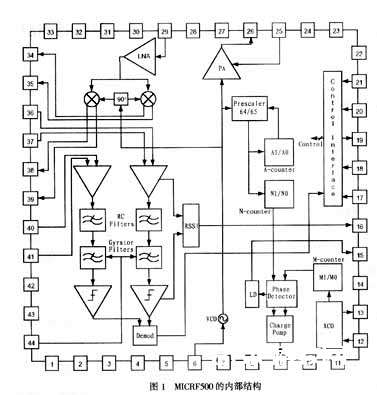

3内部结构与作业原理

MICRF500的内部结构如图1所示。该芯片内含接纳、发射和操控接口(ControlInterface)三部分。其间接纳部分由低噪声扩大器(LNA)、混频器、RC滤波器(RCFilters)、解调器(Demod)、RSSI等电路组成。发射部分由功率扩大器(PA)、预置份额分频器(Prescaler)、A计数器(Acounter)、N计数器(Ncounter)、M计数器(Mcounter)、压控振动器(VCO)、相位检波器(Phase Detector)、充电泵(Charge Pump)、晶体振动器(XCO)等电路组成。

当MICRF500处在接纳形式时,PLL合成器发生本振振动(LO)信号。N、M和A计数器给出的本振振动频率被别离存储在NO、MO和AO寄存器中。因为接纳器是零中频结构,因而用低功耗的集成低通滤波器作为通道滤波器。接纳设备中的低噪声扩大器(LNA)用于驱动正交混频器对。混频器输出馈送至两路相同的相位积分信道。每条信道包含前置扩大器、三阶Sallet-Key RC低通滤波器和限幅器。首要信道的滤波器有必要满意电路的挑选性和动态规模。

Sallen-Key RC滤波器能经过编程划分红四个不同的截止频率:10kHz、30kHz、60kHz和200kHz。经过外围电阻能够调整滤波器的截止频率。解调器可解调I和Q信道的输出并一起输出一个数字信号。当检测I和Q信道信号的相对相位时,假如I信道落后于Q信道,FSK调制频率将坐落本振振动频率之上(数据 “1”)。假如I信道信号超前Q信道信号,FSK调制频率则坐落本振振动频率之下(数据“0”)。DATAIXO脚为接纳器输出。RSSI(接纳信号强度指示器)电路可用来显现收到信号的强度等级。两头的串行接口可用于对电路进行编程。VCO谐振电路、晶体、反应电容和VCO的FSK调制元件、回路滤波器、功放和滤波器的偏置电阻等外围元器可用于RF输入输出的阻抗匹配和功率衰减。TX/RX的转化则可经过二极管来完成。

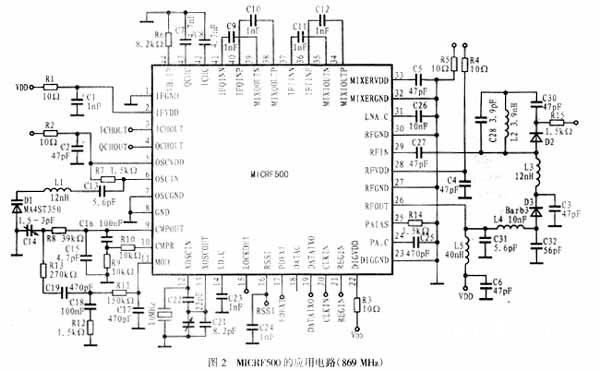

4运用电路规划

MICRF500的运用电路如图2所示,该电路的作业频率为869MHz。电路中,收发器的调制信号加到VCO,VCO和外围元件作业于869MHz。MA4ST-350-1141是MACON制作的一个专用变容二极管,而BAR63则是西门子公司出产的二极管。

因为VCO是一个根本的Colpitts振动器,因而应有一个外部谐振器和一个可变电感,谐振器可由电感L1和线性电容C13组成。

晶体振动器的晶振是RF输出频率的基准,因而要求具有很好的相位和频率安稳性。晶体振动器经过调理可变电容C20可改动谐振频率。要取得小的频偏,晶体要预老化且要有小的温度系数。本规划选用10MHz晶振。

相位检测输出被转化成电压并经14脚(LDC)外电容C23的滤波后,发生的直流电压与位Ref0-Ref5设置的基准窗口相比较。 Ref0~Ref5为1时,基准窗口在0V;Ref0~Ref5为0时,其基准窗口的直流电压最大。别的,基准窗口能在两者之间线性步进地上升或下降。窗口的大小可等效为2个(Ref6=1)基准台阶或4个(Ref6=0)基准台阶。

完成FSK有三种办法:榜首种是运用VCO完成FSK调制,其对应的发射频率将被编程在分频器A1、N1和M1中。在TX形式,DATAIXO端保持在三态,直到开端发射数据;第二种是经过开关在A、N和M分频器两组之间完成,A、N和M值对应到接纳频率和两发射频率。发射数据“0”时,将对分频器 A0、N0和M0进行编程;发射数据“1”时,将对分频器A1、N1和M1进行编程;第三种则可经过加/减1到分配器A1来完成,其频偏与比较频率持平,发射频率的校准可经过对A1、N1和M1进行编程来完成。一切类型的FSK调制数据都从引脚端DATAIXO输入。

回路滤波的规划对优化参数是很重要的,如调制速率、PLL确认时刻、带宽和相位噪声等。低位率一般可调制在PLL内,而将回路确认在不同的频率上则可经过开关分频器(M、N和A)来完成。高调制率(超越2400bps)一般靠PLL外调制来完成,规划时一般直接加到VCO。此刻,回路滤波器的值可经过软件进行编程确认。

发射功率扩大器是根本的AB类,最终一级是开集电极(OC)电路,因而应外接一负载电感(L2)。扩大器的直流电流经过外接偏置电阻R14来调整。当偏置电阻值为1.5kΩ时,偏置电流为50μA。最终一级电路的偏置电流大约为15mA。

阻抗匹配与天线的类型也有很大联系,规划时可选用最大输出功率,并在功率扩大器上接一约100Ω的阻抗。输出功率可编程为8级,每级大约相差3dB,能够经过操控字Pa2-Pa0来进行操控。

为了防备搅扰信号搅扰功放,功放应当缓慢的导通和截止。经过连接到24脚的电容C25可使偏置电流在限制规模内上升或下降。上升/下降电流典型值为 1.1μA,当电源为3V时,开关速率为2.6μs/pF。因为转化功放开关会影响PLL,所以开关速率有必要与PLL带宽相对应。

缓冲扩大器一般连接到VCO和功率扩大器之间。功率扩大器的输入信号能够扩大到希望的输出功率。经过设置位Gc为“0”能够旁路缓冲级。

RF接纳器的低搅扰扩大器可利用提高输入信号来优化频率改变进程。其首要意图是为了防备混频器搅扰。LAN是一个两级扩大器,正常时,在900MHz 处能够取得23dB的增益,LAN具有一个直流外馈环,可为LAN供给偏置。外接电容C26对一切的直流反应环路均可起到退耦和安稳效果。

经过设置ByLAN位为“1”能够旁路LAN,这对强信号对错常有用的。

混频器在900MHz有12dB增益,在34、35和38、39脚中,每一路混频器的输出阻抗约为15kΩ。

解调器解调出来的信号的频偏有必要永远比频漂大,且至少等于波特率加上频漂。

限幅器是一个零点检波器,其输出为与I-Q相位差相对应的值,波形是边际峻峭的方波。

解调器的效果是解调I和Q信道输出并发生数字量输出,一起可用来检测I和Q信道信号之间的相位差。关于I信道,在限幅器输出的每一个边缘(上升沿和下降沿),Q信道限幅器输出的振幅均被采样,反之也如此。解调器的输出经过DATAIXO引脚来完成。数据输出被IF信号每周期更新四次。假如I信道信号滞后于Q信道,FSK调制频率将坐落LO频率上方(数据“1”),而假如I信道超前Q信道,则FSK调制频率将坐落LO频率下方(数据“0”)。

解调器的输入和输出经过一阶RC低通滤波器滤波并经过斯密特触发器扩大来发生方波。在低位率时,添加引脚18的电容(DATAC)能够削减RX数据信号滤波器的带宽。滤波器的带宽有必要依据位率来进行调整,这个功用一般经过RXFilt位来操控。

RSSI(接纳信号强度指示)电路的输出与代表RF输入信号强弱的直流电压相对应。当接纳到的RF输入信号使RSSI输出添加时,RSSI将作为信号的有无指示器而用于唤醒电路。无信号时,电路将处于睡觉形式以长电池寿数。

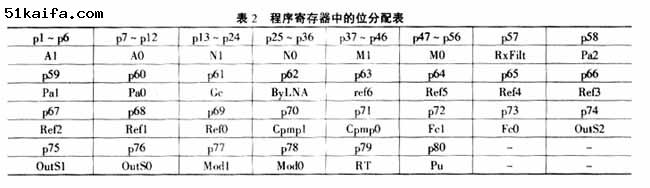

在编程时,可用两线(CLKIN和REGIN)式总线来编程电路,两线串行总线接口能够操控分频器、挑选TX的功率和RX以及合成器电路功用块,其接口由一个80位编程寄存器组成。数据和榜首有用位从REGIN线进入,榜首位输入为P1,最终一位输入为P80。程序寄存器中的位组织如表2所列。

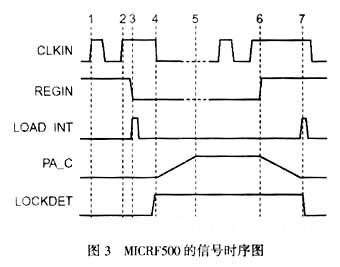

当CLKIN信号为高电平时,80位操控字首先读入移位寄存器,然后经过REGIN信号(正的或负的)装入并行寄存器。其接纳和发射形式可由电路直接指定。图3所示是MICRF500中CLKIN、REGIN、内部LOAD、INT和PA-C信号的时序图。

图3中,在时序1时,倒数第二位数据被时钟信号装入移位寄存器(‘1’);在时序2时,最终一位数据被时钟信号装入移位寄存器(‘1’);时序3时,经过REGIN信号的转化可发生一内部装入脉冲,并将操控字装入并行寄存器,从而使电路进入新的形式(TX形式),并安稳在这种新形式。在时序4时,假如时钟信号变低,功放将渐渐敞开以使RF输出信号最小。在PA敞开前,PLL处于牢靠的确认状况。而在LOCKDET被设置后,PA敞开。时序5时,功率扩大器将满负荷敞开。时序6时,一个新的操控字进入移位寄存器。当CLKIN为高时,REGIN信号发生跳变以封闭功率扩大器。时序7时,功放封闭以发生内部装入脉冲,并将新操控字装入并行寄存器,从而使电路进入一个新的形式(节电形式),但CLKIN有必要在发生内部装入脉冲后变低。当CLKIN为高时, REGIN大将不会呈现跳变,此刻,新的操控字在任何时刻内,都不影响收发器操作,它将依照自己的方法准时进 入移位寄存器。