选用双端口RAM完结DSP与PCI总线芯片之间的数据交换接口电路。

提出了一种运用CPLD处理双端口RAM地址译码和PCI接口芯片部分总线裁定的的硬件规划计划,并给出了PCI总线接口芯片寄存器装备实例,介绍了软件包WinDriver开发设备驱动程序的详细进程。

跟着核算机技术的不断发展,为满意外设间以及外设与主机间的高速数据传输,Intel公司于1991年提出了PCI总线概念。PCI总线是一种能为主CPU及外设供给高性能数据通讯的总线,其部分总线在33MHz总线时钟、32位数据通路时,数据传输速率最高可达133Mbps。实践运用中,可经过PCI总线完结主机与外部设备的高速数据传输,有用处理数据的实时传输和存储问题,为信号的实时处理打下良好基础。

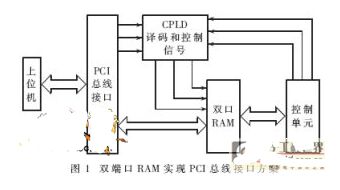

本文首要供给一种依据PCI总线的数据传输体系规划计划,其间双口RAM起桥梁效果,完结上位机与外围主控单元之间的数据握手。

1 双端口RAM完结PCI总线接口计划

本体系首要用于处理上位机与外围操控单元的数据传输问题。上位机运转信息确诊程序,经过PCI总线与外围操控单元以必定速率传输数据,在主机中实时监控并保存数据。因为完结高速实时数据传输,数据量大,所以在PCI部分总线上刺进一个高速双端口RAM。双端口RAM一端作为PCI总线接口的本地端存储器,一端作为DSP方针存储器。需求传输保存的数据经DSP处理后凭借双端口RAM和PCI总线接口完结了上位机与DSP的数据握手。本文提出的双端口RAM完结PCI总线接口计划如图1。

考虑到PCI总线接口对部分总线的操控时序比较复杂,需求译码和操控电路来完结部分总线的拜访及操控。本体系运用CPLD处理双口RAM的地址拜访竞赛抵触问题。需处理的首要问题有:①PCI接口电路规划;②CPLD地址译码和总线裁定;③PCI总线驱动程序开发。

2 PCI接口电路规划

PCI卡的规划一般选用两种计划。一种是依据PCI协议在FPGA或CPLD中完结PCI总线接口操控器,可是因为PCI协议的复杂性,使得开发难度大、周期长;另一种运用现成的PCI接口芯片,用户开发难度下降,只把要点放在PCI接口芯片部分总线的接口规划和PCI总线装备空间的初始化,而不必速度考虑PCI总线标准上很多的协议标准,加快了开发时刻。

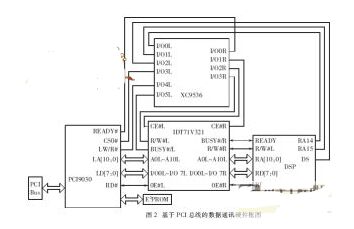

本数据传输体系运用PLX公司的PCI 9030总线接口芯片,以CPLD完结逻辑操控及与外设的衔接,整个体系的硬件框图如图 2。其间双端口RAM选用IDT71V321,CPLD选用XILINX公司的XC9536CPLD芯片,EEPROM选用NS公司的93CS56,操控单元DSP选用TMS 320LF2407A。

2.1 PCI 9030内部结构及其数据传输

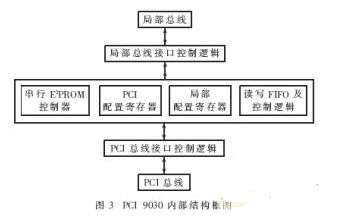

PCI 9030是PLX公司开发的PCI总线方针接口芯片。其特色:低功耗,PQFP176针封装,契合PCI V2.2标准;在PCI总线上是从设备,但在部分总线上是主设备;PCI 9030支撑突发传输,有5个PCI总线到部分总线地址空间,9个可编程的通用I/O,4个可编程的片选,支撑热插拔。PCI 9030首要由PCI总线接口逻辑、部分总线接口逻辑、串行E2PROM接口逻辑和内部逻辑组成,结构框图见图3。

PCI 9030支撑PCI主设备直接拜访部分总线上的设备,数据传输办法分为内存映射的突发传输和I/O映射的单次传输,而且由PCI基址寄存器设置在PCI内存和I/O空间中的适宜方位,别的部分映射寄存器答应PCI地址空间转换到部分地址空间。

2.2 装备实例

体系拜访的双口RAM存储空间为2KB,要求将这个存储器空间映射到部分地址空间0,选用内存办法映射,存储器的数据宽度为 8位,而且不选用突发传输,读写时不行预取。下面介绍这个地址空间各个寄存器的详细装备进程。

(1)装备地址规模寄存器

依据PCI装备寄存器与LAS0RR的对应联系以及双口RAM的地址空间800H,取7FFH的补码得到FFFFF800H。又因为依照规划要求,要映射到内存空间的任何方位而且设置为不行预取的,这样LASORR寄存器后3位应该为000H。所以LAS0RR的值应该终究确认为FFFFF800H。

(2)装备基址寄存器

该寄存器的基址有必要是地址空间规模的整数倍,在本例中有必要是2K的整数倍,可将基地址定为 00004000H,又因为基址寄存器位0为空间使能位,所以应将这一位设置1;至于位 2、位3,因为是映射到内存空间,设为00H即可。所以LAS0BA的值终究被确认为00004001H。

(3)装备片选信号操控寄存器

该寄存器的地址规模和基地址有必要与LAS0RR或LAS0BA所界说 的规模和空间相对应。可依据PCI 9030供给的装备寄存器的办法确认CS0BASE的数值:板卡的2KB空间能够用十六进制表明为800H,将800H右移一位得到400H,然后将基地址加到400H左面的任何一位中。因为所选用的基地址为00004000H,所以得到的值为00004400H;又因为第1位为片选使能位,应该设置为1。所以终究确认的数值为00004401H。

因为部分总线选用8位的宽度,将作业办法界说在不使能突发,不预取,装备总线区域描述寄存器的数值确认为400140A2H。别的,还要依据要求设置CNTRL寄存器操控PCI 9030的作业状况,确认为18784500H。当所有这些数据都装备完结后,便可将这些数据依照加载次序写入串行E2PROM中,然后完结整个体系的装备。

经过这几个寄存器的装备,一个部分地址空间便能够确认下来。在体系上电后,体系BIOS依据这几个寄存器的内容将板卡上2KB的RAM空间重映射到PCI空间中,使主机能够像拜访自己的地址空间相同拜访板卡上的RAM。

2.3 CPLD操控逻辑

关于双口RAM同一个地址单元,不能一起进行读或写操作,但两头衔接的主控芯片,都能够对其进行读、写操作,因而有必要处理地址竞赛问题。本体系中,运用XILINX公司的XC9536CPLD芯片完结PCI部分总线的译码和操控电路。因为体系操控核算首要在DSP中完结,上位机只起监控和数据保存效果,因而规则对双口RAM的操作DSP优先于PCI 9030;一起CPLD也参加了DSP片外程序存储器Flash和数据存储器RAM的地址译码,操控逻辑用公式表明为: