大多数情况下,现代电子体系规划包含规划各种元器材或许互相隔离度较近的体系。IC 的规划和管脚输出是由芯片上的电路方位决议的。封装规划师选用“扔过墙”的芯片规划,并尽或许规划较短的封装键合线,从而使封装尽或许小。然后 PCB 规划师,一般一向天怒人怨,拿起封装 IC,费尽心机找出布线信号的办法,而这看上去总像是错放在某个管脚或焊球上。

跟着现在 SoC 杂乱程度的不断添加,以及多芯片封装的开展,各公司已开端知道到 IC、封装基底和 PCB 规划组之间穿插范畴协作的价值。因为高管脚数目器材具有本钱敏感性这一特色,工程师不得不重新考虑在对杂乱的 IC 封装变量进行折衷的一起,怎么规划和优化芯片的 I/O 布局。而且针对多个板级渠道进行所有这些作业。现在,各种东西的呈现让封装和 PCB 的规划成为一个协作、彼此获益的进程。

认知规划

要最大程度地发挥作用,EDA 东西应当清楚知道会在其他进程中用到的东西。在封装和PCB 规划范畴,彼此之间的知道很少。固然,FPGA 管脚输出可以在必定范围内由用户界说,但“规范”元件一般没有这样的选项。

让东西清楚规划及产品规划到工艺流程中的其他环节,这些东西就能在更短的时刻内协作并交支付更好的体系规划。此外,规范 IC 芯片能以不同办法封装,这取决于终端产品的外形参数,从而为各种办法完成更为优化的解决计划。

东西之间怎么快速地进行彼此认知,然后协作交支付更优的规划呢?运用相同 CPU 芯片的智能手机和平板电脑的规划便可以完美地阐明这一形式。明显,许多移动设备公司正在进行这样的测验。

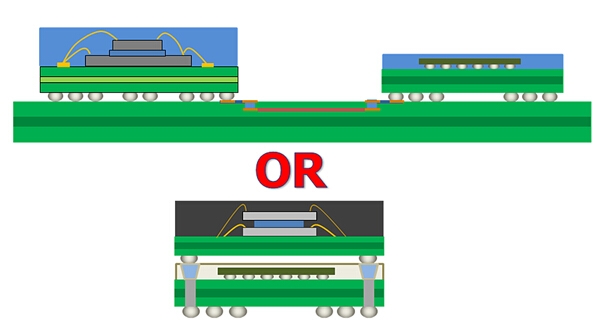

但是,比较智能手机,平板电脑的PCB基板上可用面积明显更大,其束缚也更少。因而,平板电脑上的 CPU 封装或许更大,有不同的管脚输出,或许或许比智能手机上的 CPU 功耗更大功率。因而,单个“规范”封装或许并非最佳运用封装(图 1)。

图 1:平板电脑规划或许有更多可用的基板面积布局 CPU 和胶接电路,使上层封装进行运作。但关于运用相同 CPU 的智能手机而言,这种办法空间要求过大,因而更好的解决计划是运用基层封装。

现在,运用新东西,规划师能装备芯片,从封装的视角“看看”规划,再转移到 PCB(传统办法),或先了解 PCB 规划要求,再返回到封装规划中。而且,他们能拿到每个运用该 CPU 的产品,再从 PCB 回过头来规划专门为此进行规划优化的最佳封装。

从封装观念来看,物理规划规矩由 PCB 规划要求决议。然后,东西与规矩和封装规划师交互协作,交支付适用于该芯片特定运用的最佳封装。这种相对较快的封装规划办法还能探究不同的构思,以快速找到最佳计划。

实在事例

图 2 为假定的产品规划。在这个比如中,终究产品的外形参数已知,元器材也已进行开端布局。留意顶部的阐明,已预留布局 CPU 的方位。运用这种输入,东西可以开端途径查找,即根据 PCB 规划师和封装规划师编写的规矩,测验多种封装装备。

图 2:一般,物理外形参数是产品规划的首要束缚。运用途径查找东西,封装和 PCB 规划师能协作找到物理规划束缚内的最佳封装,并可简化杂乱封装的扇出和布线。

关于每种规划,可以在 PCB 上进行传统布线,以决议最佳的封装和管脚输出。规矩答应规划师界说各种参数,如未运用的输出角落管脚,让差分对连在一起,分配电源和接地的办法,以及处理数据和地址总线的办法等。

一旦确认规矩,就不仅仅“按下按钮再坐回去”,而是比运用电子表格和管脚列表愈加直接、愈加快速、愈加精确,这便是现状。

长处

东西认知规划具有明显的长处,而且其可以在任何规划范畴中进行规划优化。首要,其能愈加容易地定制多个封装规划,以便依照所需的外形参数最佳地使用给定的元器材。然后从多个“假定剖析”情境审视规划,如更小的封装、更少的本钱、最简略的扇出和出口等。其次,因为存在很多管脚,使用电子表格和管脚列表进行封装规划就显得无能为力。当人工输入数以百计的管脚数据时,过错率简直为 100%。当然,其长处还包含:质量的进步、取得合适外形参数的最佳封装、过错的削减以及在整个体系规划中节约很多的时刻。