关于需求在PCB板上运用大规模FPGA器材的规划人员来说,I/O引脚分配是有必要面临的很多应战之一。 由于很多原因,许多规划人员宣布为大型FPGA器材和高档BGA封装确认I/O引脚装备或布局计划越来越困难。 可是组合运用多种智能I/O规划东西,可以使引脚分配进程变得更轻松。

在PCB上界说FPGA器材的I/O引脚布局是一项艰巨的规划应战,即或许协助规划快速完结,也有或许形成规划失利。 在此进程中有必要平衡FPGA 和 PCB两方面的要求,一起还要并行完结两者的规划。 假如仅仅针对PCB或FPGA进行引脚布局优化,那么或许在另一方面引起规划问题。

为了解引脚分配所引起的成果,需求以可视化办法显现出PCB布局和FPGA物理器材引脚,以及内部FPGA I/O点和相关资源。 不幸的是,到今天为止还没有单个东西或办法可以一起满意一切这些协同规划需求。

但是,可以结合不同的技能和战略来优化引脚规划流程并活跃选用Xilinx PinAhead技能等新协同规划东西来开展出一套有用的引脚分配和布局办法。 赛灵思公司在ISE软件规划套件10.1版中包括了PinAhead。

赛灵思公司开发了一种规矩驱动的办法。首要依据PCB和FPGA规划要求界说一套初始引脚布局,这样运用与终究版别十分挨近的引脚布局规划小组就可以尽或许早地开端各自的规划流程。 假如在规划流程的后期由于PCB布线或内部FPGA功用问题而需求进行调整,在选用这一办法晨这些问题一般也现已部分化了,只需求在PCB或FPGA规划中进行很小的规划修正。

进程1: 评价规划参数

那么,从哪里开端呢? 首要应当尽早拟定I/O分配战略。 但没有优化东西或完好的网表,完结这一使命或许很困难。

首要,让咱们先答复几个问题来确认PCB物理参数和束缚:

* PCB板有几层、走线宽度以及过孔尺度多大?

* PCB参数对可运用的FPGA封装类型(如BGA)有束缚吗?

* PCB上有没有FPGA有必要运用的固定接口方位? 其它芯片、衔接器或布局束缚?

* 哪些高速接口需求特别重视?

能否将布局战略可视化,然后确保最短互连?

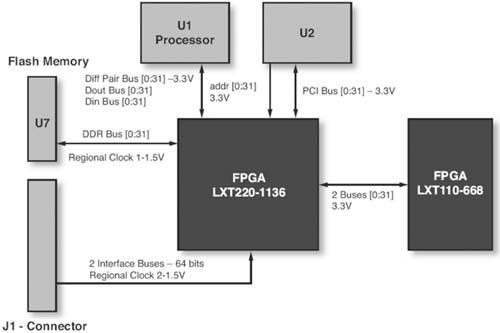

你会发现画一张PCB布局图很有协助。PCB布局图上应当包括一切首要元器材以及要害接口和总线,然后可以协助确认最佳的FPGA引脚分配。 请注意将元器材画在PCB板的实践装置面上。 标示出需求特别重视的接口,如高速总线和差分对(图1)。

下一步,查看FPGA器材的布局来了解芯片上的物理资源地点。 列出规划中运用的不同电压和时钟,开端阻隔规划需求的接口。 然后确认规划是否运用特别的I/O接口资源,如千兆收发器(GT)、BUFR、IODELAY以及数字时钟办理器。这些资源或许需求将有关的I/O引脚布署得尽量相互挨近。

现在需求确认规划中运用的PowerPC、DSP48和RAM16等FPGA资源的方位。 将衔接到I/O组的任何相关I/O尽量置于尽相关资源最近的当地。 然后看一下能否将某些I/O信号组合到接口,这关于引脚分配很有协助。 终究,确认FPGA的装备办法。

图1 PCB衔接图

进程2: 界说引脚布局要求

一旦了解了首要的FPGA接口并创立了物理布局的原型,就可以界说引脚布局了。 有些规划人员喜爱运用包括一切I/O信号数据表来坚持与引脚的对应。 你可以按电压、时钟、接口或总线对它们进行分组。 这一办法的确十分有用,由于它可协助你将信号组合成组,然后在分配引脚时可以按组进行。 这一阶段,你还会发现为了完结最优PCB布线,有些要害接口有必要置于器材的某个边,或许运用外部物理引脚。

在考虑到FPGA和PCB要求并确认了首要的接口方位今后,下一步是依据一切这些条件将引脚分配给I/O组。 这也是真实开端作业的当地。 在当时的规划流程中,引脚分配时一项消耗时刻的使命,在处理任何功用和信号完好性问题的进程中或许会触及许多测验和过错。 传统上,规划人员都是徒手画图来完结这项使命的,由于EDA和芯片供货商没有供给协助规划人员将FPGA和PCB引脚布局可视化的东西。

但现在赛灵思公司供给了相应的东西。 在ISE Foundation软件东西10.1版别中包括的PlanAhead Lite是PlanAhead规划、剖析和平面布局东西的简化版。 其间包括的针对PCB 和 FPGA规划的PinAhead的东西使得I/O引脚装备更为简单。

这儿咱们不计划具体介绍该东西的一切细节,而仅仅看一下怎么将其用于I/O引脚分配。 假如你期望了解PinAhead的更具体信息,包括视频展现和教程,请拜访 www.xilinx.com/planahead。

进程3: 运用PinAhead进行引脚分配

PinAhead环境供给了一组不同的视图。运用这些视图可以协助完结I/O端口信息与物理封装引脚或裸片I/O盘(Pad)的对应和分配(图2)。

PinAhead的图形环境与PlanAhead相似,在器材视图中明晰地显现出芯片上的I/O盘和相关资源,并在封装视图中显现出物理器材引脚。 视图一起显现出I/O端口和物理引脚信息,这样可以经过穿插选取来打听逻辑规划和物理器材资源的对应。

你可以在没有规划网表的状况下运用PinAhead来测验器材资源,或许直接开端I/O引脚规划流程。 封装引脚视图(“Package Pins” view)依据器材数据表列出了器材封装技能参数,因而大多数状况下在进行引脚装备时都不再需求去参阅器材数据手册。 封装引脚视图以列表办法对I/O组(bank)进行了分类,因而可以一起在器材和封装视图中穿插挑选和高亮显现I/O组。 视频明晰显现出物理引脚方位和裸片中的I/O盘的联系,然后简化了I/O组的优化挑选。 封装引脚视频还显现了I/O组中每一引脚的信息。

你可以运用PinAhead接口从头开端创立I/O端口,也可以从CSV格局数据表、HDL源文件头或归纳后的网络和UCF格局束缚文件中导入I/O端口。 I/O端口视图(“I/O Ports” view)显现出规划中界说的一切I/O端口信号,总线文件夹则显现分组的总线和差分对信号。

你可以按不同办法对封装引脚和I/O端口视图进行排序。 可以切换列表视图显现根据分类的列表或悉数列表,或许点击鼠标对封装引脚视图进行排序,显现一切可用的大局时钟或区域时钟引脚。 一起还可以将信息导出到CSV格局数据表,做为引脚装备的起点。

PinAhead还供给了一个界面,支撑有挑选地制止PinAhead将I/O端口分配给某些I/O引脚、I/O引脚组或I/O组。 可以在封装引脚、器材或封装视图中挑选和制止引脚。 例如,你可以对封装引脚视图(Package Pins view)排序并制止一切VREF引脚。

PinAhead答应将相关的I/O端口和总线组合为“接口”(interface)。 这样组合使你可以将相关I/O端口做为单个实体处理,然后简化了I/O端口办理和分配使命。 接口组合功用可以更简单地可视化显现和办理与特定逻辑接口相关联的一切信号。

可便利地在规划间复制接口,或许运用接口组合生成特定接口的PCB原理图符号。 组合后的接口在I/O端口视图中以可扩展文件夹的办法呈现,经过在视图中挑选I/O端口并将其拖动到接口文件夹,可以将额定的I/O端口添加到接口组合中。

当创立I/O端口时,可将其分配到封装引脚或I/O盘(pad)。 在此之前,最好先查看一下I/O端口的开端PCB互连草图并与PCB规划人员洽谈,了解布放不同I/O端口接口的相关方位和其它需考虑的要素。 恰当的总线次序和边际间隔有PCB布线十分有协助,可以大大节省规划时刻。

经过将单个引脚、总线和接口拖动到器材或封装视图,可以将它们分配到I/O引脚。 运用不同的分配办法,可以将引脚组分配给选定的I/O引脚。 可用的办法包括“Place I/O Ports in an I/O Bank,” “Place I/O Ports in Area,” 以及 “Place I/O Ports Sequentially.”。

每种办法供给了将I/O端口分配到引脚的不同分配办法。 运用这些办法,可以经过鼠标光标处弹出的窗口了解你所分配的端口数量信息。 直到分配了一切选定I/O端口之前,这一办法一向坚持。

器材视图(Device view)以图形办法显现一切时钟区域和时钟相关的逻辑目标,然后使时钟相关的I/O分配更简单、更直观。 挑选一个时钟区将会显现一切I/O组、时钟相关的资源以及与其相关的器材资源。

PlanAhead软件企图确保你在引脚分配时一直契合规矩。 在你的指引下,PlanAhead东西将差分以端口分配给恰当的引脚对。 当交互式指定I/O端口时,东西会运转规矩查看(DRC)来确保布局是符合规矩的。

东西缺省设置运转在交互DRC办法,当然你也可以挑选封闭这一办法。 东西会查看电压抵触、VREF引脚或I/O规范抵触,以及坐落GT器材邻近的噪声灵敏引脚。 当发现过错或问题时,东西会显现一条提示信息(Tooltip),告知你为什么不可以将某个I/O端口分配给特定的引脚。

经过激活 PinAhead的 “Autoplace”指令,还可以让其主动分配一切或任何挑选的I/O端口到封装引脚。 Autoplace指令将会恪守一切I/O规范和差分对规矩,并正确布署大局时钟引脚。 该指令还会测验尽量将I/O端口组合为接口(interface)。

器材视图(Device view)以图形办法显现一切时钟区域和时钟相关的逻辑目标,然后使时钟相关的I/O分配更简单、更直观。 挑选一个时钟区将会显现一切I/O组、时钟相关的资源以及与其相关的器材资源。 经过可用资源与其物理联系的探究,区域时钟规划进程变得更简单。

还可运用PinAhead布局规划中其它与I/O相关的逻辑,如BUFG、BUFR、IODELAY、 IDELAYCTRL和DCM。 运用PlanAhead中的“Find”指令,可以便利地定位这些目标和布放点。 要想有挑选地观察的扩展逻辑和逻辑衔接,请运用东西中的原理图视图(“Schematic” view)。

经过在PlanAhead软件中的某个视图中挑选特定的I/O相关逻辑并将其拖动到器材视图(Device view)中的选定方位,就可以确定其布局。

PlanAhead软件将会主动判别,仅答应将有关逻辑放在适宜的方位。 在拖动规划中的逻辑目标时,动态光标会显现出恰当的布局方位。

进程4: 为终究核签(Sign-Off)运转DRC和WASSO

一旦完结引脚分配,就可运用 PinAhead丰厚的DRC规矩来进行核签前的DRC查看,确保在运转PlanAhead软件施行东西前规划是无错的。 东西中的很多I/O和时钟相关规矩可确保I/O布局是合法的。 可运用PlanAhead的DRC对话框来挑选相应的规矩。

假如东西发现违背规矩的状况,将会显现带有过错信息的DRC成果表。 挑选相应的过错信息可以更进一步入地了解有关状况。

PlanAhead还供给了加权均匀同步转化输出(WASSO)剖析功用,可协助辨认引脚分配引起的潜在信号完好性问题。 为东西供给PCB规划的寄生参数特性,PlanAhead软件将会剖析不同的I/O组以及其近邻,并陈述每一I/O组的运用状况和状况。

进程5: 导出I/O引脚分配数据

你可以将I/O端口列表和封装引脚信息从PlanAhead软件导出为CSV格局文件、HDL头或UCF文件。 CSV文件包括有关器材封装引脚的一切信息,以及与规划相关的I/O引脚分配和装备。 列表中的封装引脚部分是数据表中界说I/O端口的很好起点。

你还可以运用该数据表主动生成规划小组开端PCB布局所需求的PCB原理图符号。 但是,有时这些符号关于原理图来说太长了,或许需求将它们缩短为几个符号。 运用PinAhead中的创立的接口组可以快速做到这一点。

以原理图符号办法供给这些I/O引脚装备为PCB规划人员开端PCB布局供给了很好的根底。 由于假如在引脚分配的开端就考虑到PCB接口,那么最很或许与终究的引脚装备比较挨近。

假如的确需求改动引脚来便利布线,那么改动也比较简单,由于需求改动的引脚或许现已在I/O组内了。 这种办法不会对FPGA规划形成太大的影响。 经过在PCB和FPGA规划人员之间传递修正过的引脚布局数据表或UCF文件,可以确保两个部分之间的任何修正是同步的。

为避免信号噪声以及支撑某些FPGA功用,你还或许期望将未用的引脚或特定装备的引脚衔接到VCC或GND。 赛灵思现在正在致力于在PinAhead的下一版别中供给这一功用。经过一个界面便利FPGA规划人员辅导此类引脚,并在输出的CSV数据表中包括相应的引脚衔接。 这样PCB规划人员就可以更简单辨认相关引脚并正确衔接之。

未来,跟着FPGA集成更杂乱的功用以及运用更先进的封装,开展牢靠的FPGA和PCB引脚布局办法势在必行。 PinAhead Lite在协助完结根据协同规划理念的引脚布局战略方面现已可以供给很大协助,但咱们依然现已在致力于改善这一东西以协助规划人员更好地应对引脚布局方面的应战。

图 2 PinAhead 环境