S3C2440的时钟操控单元可以发生如下的时钟信号:FCLK FOR CPU, HCLK FOR AHB BUS(高速设备,比方内存操控器、中止操控器、LCD操控器、DMA以及USBhost), PCLK FOR APB BUS(低速设备,比方WTG、I2C,SDI/MMC,GPIO,RTC,UART,PWM,ADC,SPI)和用于USB的UCLK,共四种分频率,前三种共用一个PLL。 S3C2440有两个PLL, 一个用于FCLK,HCLK,和PCLK,叫做MPLL; 而另一个用于USB模块(固定48MHz),叫做UPLL。时钟操控逻辑还可以没有PLL来下降时钟或许不使每个外设衔接到时钟以下降电源能耗。

————————————-o———————————————————

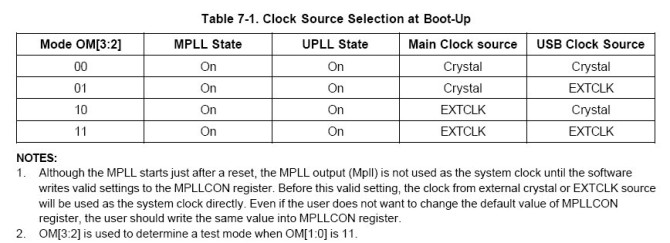

关于时钟源挑选的问题,首要时钟源一个来自于外部晶振(XTlpll),一个来自于外部时钟(EXTCLK)。时钟发生器包含一个衔接到外部晶振的振荡器和两个锁相环(PLL)。 时钟源的挑选可以经过芯片引脚的状况进行装备,即芯片的OM3和OM2引脚。具体分配状况如下表所示:(原理图中现已将OM3和OM2都接地,即00的状况,用的是外部晶振,并且晶振频率为12MHz)。.

—————————o—————————————————–

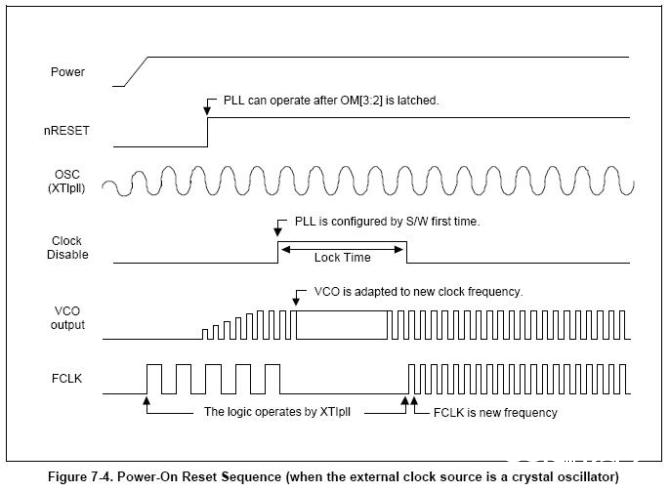

具体分频寄存器设置时序如下图所示:(虽然MPLL在系统复位的时分就开端发生,可是只要有用的设置好MPLLCON寄存器后才干用于系统时钟。在此之前,外部时钟将直接作为系统时钟。即便不需求改动MPLLCON寄存器的初值,也有必要将相同的值写入寄存器。设置完成后,经过LOCKTIME的时刻,设置的分频才干起作用。)

如上图所示,FCLK的发动进程:

1、上电几毫秒后,晶振输出安稳,FCLK=晶振频率,nRESET信号康复高电平后,CPU开端履行指令。

2、咱们可以在程序最初发动MPLL,在设置MPLL的几个寄存器后,需求等候一段时刻(Lock Time),MPLL的输出才安稳。在这段时刻(Lock Time)内,FCLK停振,CPU停止作业。Lock Time的长短由寄存器LOCKTIME设定。

3、Lock Time之后,MPLL输出正常,CPU作业在新的FCLK下。LOCKTIME默许时刻为200us。

—————————————–o————————————————-

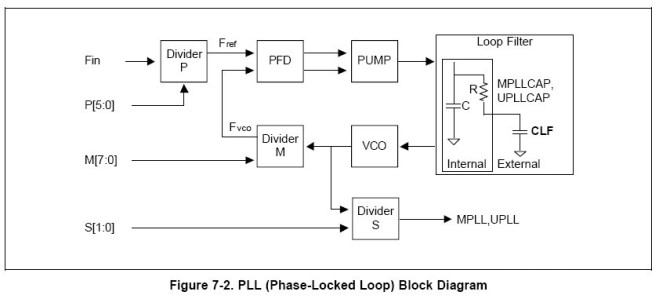

时钟分频流程如下图所示:(Fin默许为外部晶振时钟频率,12MHz。)

坐落时钟信号发生器的内部MPLL用于将输出信号和相关输入信号在相位和频率上同步起来。包含上图所示的一些根本模块:依据DC电压发生相应份额联系频率的压控振荡器VCO,出版P(对输入频率Fin进行分频),除数M(对VCO的输出频率进行M分频,分频后输入到相位频率探测器PFD),除数S(对MPLL输出频率Mpll进行分频),相差探测器,charge pump,loop filter。

—————————-o————————————————

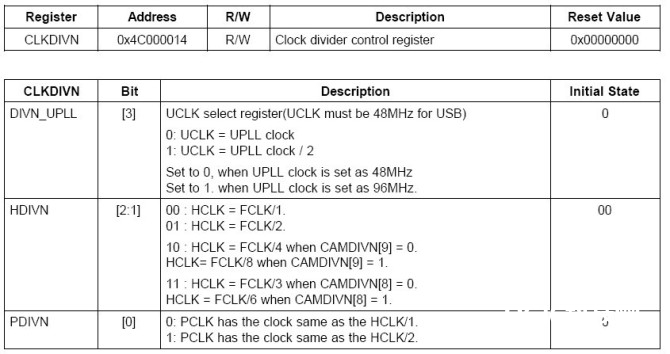

时钟频率的核算联系:FCLK,HCLK,PCLK.(其间现已知道用于USB的UCLK位48MHz。)

一般状况下,这三个一直之间是存在必定的额份额联系的,默许状况下为1:1:1。可是通常状况下会设置为1:4:8或许1:3:6。寄存器CLKDIVN用于设置这三者之间的份额联系。

也便是说,假如CLKDIVN设置为0x5,那么份额即为1:4:8,条件是CAMDIVN[9]为0.也就说假如主频FLCK是400MHz,依照1:4:8的设置,那么HLCK是100MHz,PLCK是50MHz。讲到这儿主题也该杰出,提到最终,问题的要害便是怎么核算FCLK了吧!!!

——————————–ooo——————————————

现在的CPU主频都是经过倍频的技能完成的,下面就描绘下怎么个倍频法:

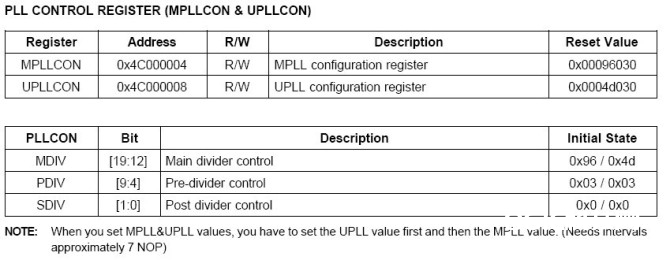

1. MPLL. 关于S3C2440来说,常用的输入Fin首要有两种频率:12MHz和16.935MHz。CPU经过MDIV、PDIV和SDIV进行倍频得到MPLL,即FCLK。公式如下所示:

Mpll = (2 * m * Fin) / (p * 2^S)

m = (MDIV + 8), p = (PDIV + 2), s = SDIV; 1<=M<=248,1<=P<=62

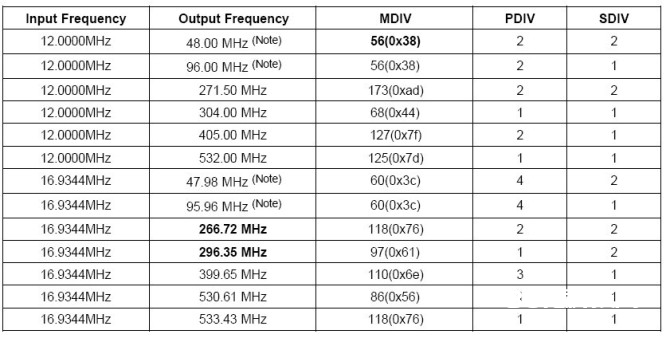

理论上,咱们可以经过设置恣意值而得到咱们想要的频率,但是因为实践存在种种的束缚联系,设置一个恰当的频率不容易,手册中引荐了如下的设置值:

例如,假定输入时钟FIN=16.9344M,MDIV=110, PDIV=3, SDIV=1,运用上面的公式,FCLK=2*16.9344*(110+8)/((2+3)*2)=399.65 MHz。

2. UPLL.上面现已具体的描绘了MPLL的设置进程。下面侧重描绘USB的运用频率UPLL的设置。需求对UPLLCON寄存器设置,如上上图所示。相同也可以经过查表。

Upll = (m * Fin) / (p * 2^S)

m = (MDIV + 8), p = (PDIV + 2), s = SDIV

需求留意的是CLKDIVN寄存器的第三位DIVN_UPLL用来设置USB时钟UCLK和UPLL的联系,假如UPLL现已是48Mhz了,那么这一位应该设置为0,表明1:1的联系,否则是1:2的联系。因为方针USB只需求48MHz的频率,所以源频率,即UPLL只能为48或许96。

——————————–ooo——————————————

讲到这儿,要点都说了哇,不多还有些特别的东西需求提出来下。

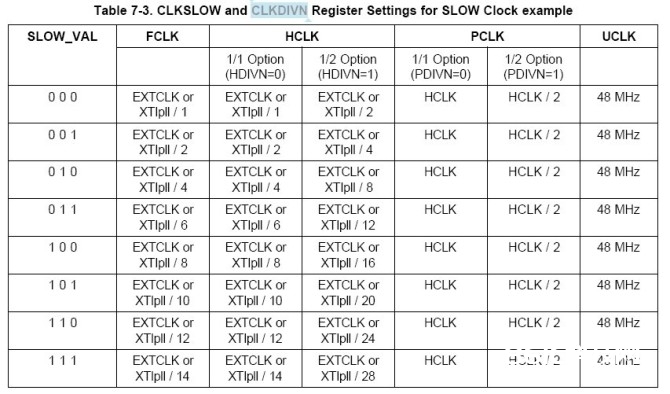

1. 在arm的系统中,还存在一个概念,叫做慢时钟形式的概念,行将时钟折半或许封闭,以削减能源耗费。可以经过CLKSLOW和CLKDIVN寄存器相互配合完成。如下图所示:

2. arm系统中许多模块都需求时钟,要是可以将不需求运用时钟的外设的时钟共用给关了,也能削减耗费,在arm中供给了这样的寄存器给予定制,即CLKCON寄存器。

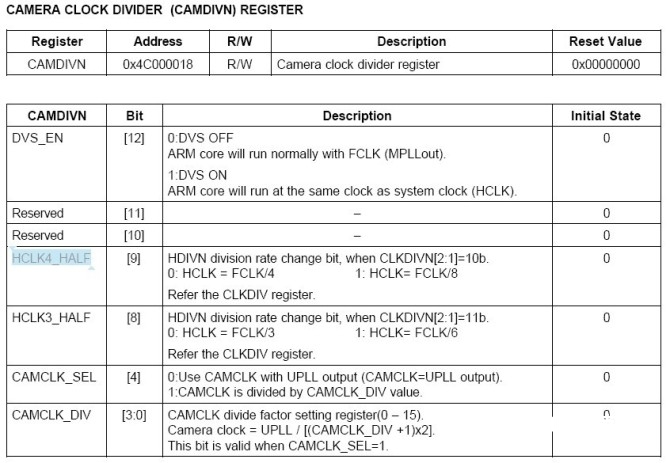

3. 专门用于相机时钟设定的寄存器CAMDIVN。如下图所示,在分频时分用到了HCLK4_HALF、HCLK3_HALF。

没了~~~

————over—————————————-

样例程序如下:

[PLL_ON_START; //设置CLKDIVN的值在PLL锁存时刻LOCKTIME之后有用。

;Configure FCLK:HCLK:PCLK

ldrr0,=CLKDIVN

ldrr1,=CLKDIV_VAL;CLKDIV_VAL=7,7=1:3:6. Fclk:Hclk:Pclk

strr1,[r0]

;Configure UPLL //UPLL

ldrr0,=UPLLCON

ldrr1,=((U_MDIV<<12)+(U_PDIV<<4)+U_SDIV) ; //Fin = 12.0MHz, UCLK = 48MHz

strr1,[r0]

;Configure MPLL //MPLL

ldrr0,=MPLLCON

ldrr1,=((M_MDIV<<12)+(M_PDIV<<4)+M_SDIV) ; //Fin = 12.0MHz, FCLK = 400MHz

strr1,[r0]

]

END.!!!