摘要 介绍一种16通道便携式逻辑剖析仪,经过FPGA将高速数据采样并缓存,选用USB操控芯片和FPCA协同操控将数据经过USB接口发送到电脑的上位机上显现,简化了以往逻辑剖析仪硬件电路部分,降低了逻辑剖析仪的本钱且便于带着。要点论述硬件电路部分的规划。

关键词 逻辑剖析仪;USB接口;FPGA;FIFO传输

逻辑剖析仪是数字规划验证与调试进程中运用广泛的东西,其能够查验数字电路是否正常作业,并协助用户查找并排除故障。每次可捕获并显现多个信号,剖析这些信号的时刻联系和逻辑联系。依据硬件设备规划上的差异,现在逻辑剖析仪大致可分为独立式和需结合电脑的卡式虚拟逻辑剖析仪。独立式逻辑剖析仪功用优异,但价格昂贵,一般用户较少运用。而本项目所完结的便携式逻辑剖析仪,以较低的本钱供给了相应的功用,尽管功用有所下降,但完全能够满意一般的逻辑信号剖析,而且使本钱大幅度下降,仪器体积较小,便于带着,合适普通用户的运用。

1 体系整体规划方案

本逻辑剖析仪可完结16通道逻辑剖析,输入信号可所以模拟信号或数字信号;可丈量宽规模输入电平,支撑1.8~5 V电平采样;选用芯片CY7C68013A作为主控芯片,经过USB 2.0将其与电脑衔接传输数据信息,运用FPGA完结高采样速率,每通道都支撑12 Mbit·s-1高速采样;被采样的信号按次序存储在存储器中。采样信息以“先进先出”的准则安排在存储器中,得到显现指令后,依照先后次序逐个读出信息,按设定的显现方法进行被丈量的显现。这样就能够在软件界面观测到所需求的数字波形,并可设置触发方法,显现所需求的波形。

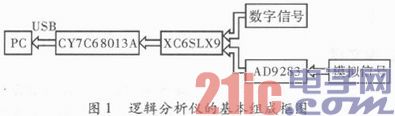

本项目选用CY7C68013A作为USB收集主控芯片,运用XC6SLX9作为数据通道的挑选器材,挑选输入到CY7C68013A的数据是来源于数字信号仍是模拟信号经ADC模块之后的数字信号。因为该逻辑剖析仪为USB衔接,故此在USB衔接端口上参加ESD芯片。并在板上添加16 kB的EEPR0M来作为CY7C68013A的程序存储器。图1为逻辑剖析仪的根本组成框图。

项目所选用的CY7C68013A芯片为低功耗芯片,该芯片内核为增强型51核,内部有16 kB程序数据区,该芯片的主频为48 MHz,而且满意480 Mbit·s-1高速传输协议标准,契合USB2.0标准,并向下兼容USB1.1标准,根本能满意该项意图数据要求。

XC6SLX9为Xilinx公司出产的Spartan6系列的FPGA,具有9 152个逻辑单元。Spartan6系列产品根据公认的低功耗45 nm、9-金属铜层、双栅极氧化层工艺技能,供给了高档功耗办理技能、150 000个逻辑单元、集成式PCI Express模块、高档存储器支撑、250 MHz DSP Slice和3.125Gbit·s-1低功耗收发器。该项目所选用的芯片为144脚封装的芯片,所具有的IO能够满意数据高速通讯的要求。

在USB衔接端参加ESD芯片能够更好的避免静电搅扰,使得该逻辑剖析仪运用起来愈加安全可靠。

2 硬件电路规划

体系硬件规划首要包含与计算机接口部分和数据收集部分。经过FPGA完结触发设置,高速捕获数据和缓存的操控,运用CY7C68013A作为USB主控芯片完结与上位机的通讯,将数据发送到计算机上位机上,而且接纳上位机发送回的触发操控字及其他操控信息,与FPGA协同作业。电路分为USB主控模块,FPGA从控模块,数据收集模块,数据缓存模块,电源供电模块这5大模块。

2.1 USB主控模块

USB主控芯片挑选的类型是CY7C68013A-56PVXC,该芯片集成USB 2.0收发器、增强型8051微处理器,适用性、外观和功用均与FX2兼容。具有16 kB片上代码/数据RAM,4个可编程的BULK/INTERRUPT/ISOCHRONOUS端点,8位或16位外部数据接口,且它的可编程接口可与大多数并行接口直接衔接、由可编程波形描述符和装备寄存器界说波形、支撑多个RDY和CTL输出,该芯片的作业电压为3.3 V,容限电压为5 V,集成I2C操控器。

USB主控芯片接24 MHz晶振,PB口接纳来自于FPGA的FIFO数据,15脚和16脚接USB_B型接口的D+和D-,用于向上位机发送数据,一起接纳上位机操控信息。I2C总线上接一AT24C64(EEPROM)用做USB程序存储器。其他的引脚用于读取FPGA的当时状况和发送触发等信息给FPGA,以确认何时进行读取数据。

2.2 FPGA从控模块

FPGA选用Xilinx Spartan-6系列的XC6SLX9-4TQ144C,接100 MHz的晶振。芯片中设定的16个IO引脚接纳来自于74ALVC164245的16位三态总线收发器的数据,FPGA.VS[2:0]三引脚悉数拉高,装备为快速读写形式,能够进步采样速率。Spartan-6系列FPGA中,装备形式引脚为M[1:0],不像Spartan-3系列有3个装备引脚M[2:0],这儿装备为“10”,即主串形式。此刻INIT_B引脚需求拉高,避免芯片装备完结后又进入芯片初始化,DONE引脚也要拉高。装备JTAG接口用于下载程序。其他引脚用于衔接两片4 MB的RAM,用于将收集到的数据先缓存进RAM中。

2.3 数据收集模块

数据收集芯片选用SN74LVC16245ADGGR,是一个16位三态总线收发器。当OE引脚接高电平时,输出为高阻态。当OE为低时,假如DIR引脚为低电平,则数据从B口传向A口,DIR为高电平时,数据从A口传向B口。图顶用B口收集外部数据,而且外接1MΩ电阻以进步输入阻抗。因而DIR和OE引脚接上拉电阻,默许上电从A到B输出无效。

2.4 数据缓存模块

扩展RAM芯片选用的是256×16 kbit高速异步CMOS静态RAM芯片IS61LV25616。直接将nCE,nLB,nUB这3个引脚接CND,能够便利读写数据。读写操控信号nOE和nWE与FPGA相连,用于操控将外部收集数据读入RAM缓存或将数据读出经过USB操控芯片传送到上位机中。其操控逻辑为:nWE为高,nOE为低时,从RAM中读出数据;nWE为低时,写入数据到RAM中。

2.5 电源供电模块

供电芯片挑选的是LM1117系列稳压芯片,有3.3 V和1.2 V。电源输入选用的是耳机式插孔电源,输入为5 V,1 A。假如用USB供电,因为USB最大输出电流为500 mA,因而在高速采样时或许电流不行,因而选用外接电源。

3 逻辑剖析仪的规划验证

逻辑剖析仪的上位机软件选用Saleae Logic1.1.16。装上软件和驱动之后,还要给USB主控芯片CY7C68013A烧写固件程序,Saleae供给了一个iic文件,用于和Saleae Logic上位机软件进行通讯。FPGA的逻辑代码包含USB协同操控部分,SRAM缓存部分,触发设置挑选部分,FIFO数据收集部分,归纳编译后生成bit文件,用Xilinx Impact软件烧写进FPGA的Flash中,FPGA就能够主动完结上电装备进程,无需再下载。图2为测验截图。能够看出,软件左上端能够挑选采样速率和深度,左端能够进行触发设置,设置好后,点击Start后就能够收集数据,右端能够显现具体的丈量信息。

4 结束语

规划的便携式逻辑剖析仪本钱低价,能够完结16通道的数据采样,触发设置。能够完结3通道90 MHz最高采样率,6通道50 MHz最高采样率,9通道30MHz最高采样率以及16通道12 MHz最高采样率。软件操作界面简略易懂,简单上手运用,能够满意一般的科研和教育的要求。