在上SDSoC系列文章的上一篇中,咱们现已介绍了如安在SDSoC中构建硬件和软件渠道,并运用SDSPFM东西生成客户运用开发渠道(拜见《SDSoC开发起步:构建硬件和软件渠道》)。假如你现已完结了上述作业,祝贺你——现在你可以正式“起步”开端依据SDSoC在Zynq SoC上开发自己的运用了!

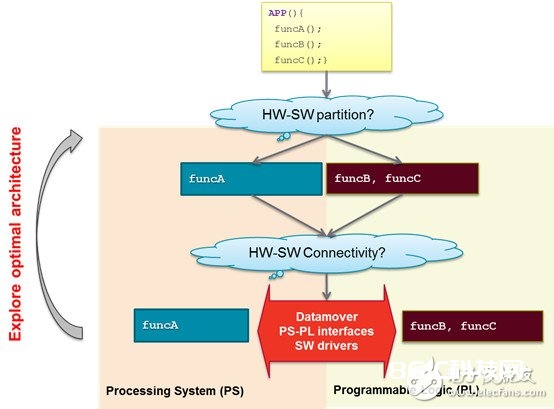

一个典型的SDSoC规划开发流程,包含以下几个过程:

用户界说开发运用所需的方针渠道。

用户依据C/C++规划和验证算法。

用户依据体系特征描述确认功用瓶颈,然后进行软硬件分区。

SDSoC将主动履行那些经过PL(可编程逻辑)加快的功用,其他功用保留在PS(处理器体系)中。

SDSoC也将主动生成软/硬件之间的衔接和DataMover逻辑以衔接PL和PS中的功用。

假如终究的成果未到达规划要求,开发者可以从头进行软硬件功用分区,探究最优的体系架构。

图1,SDSoC典型开发流程(图片来历:赛灵思)

没错,运用SDSoC进行运用开发说起来便是这么简略的几步。咱们这篇文章的内容完全可以在这里划上句号。

不过,咱们仍是期望将现在“简略”的规划流程,和传统上可编程逻辑“不简略”的规划流程进行一个比照,让我们深入认识到SDSoC究竟帮你做了些什么?

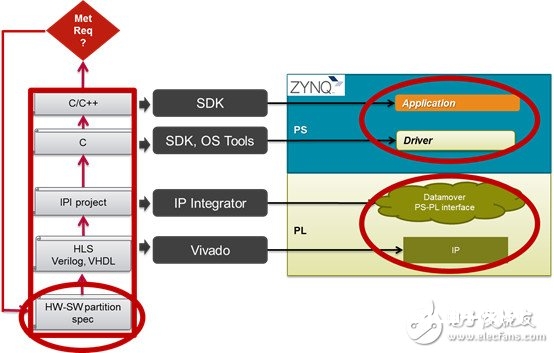

所谓“没有比照就没有损伤”,传统的Zynq SoC开发流程是杂乱成这个姿态的——首先由体系架构工程师对软硬件进行分区,即确认哪些功用放入PL(可编程逻辑)中进行硬件加快,哪些功用在PS(处理器体系)顶用软件完结;

接下来,硬件工程师依据Vivado生成要在PL中加快的IP并建立硬件渠道,还要完结软/硬件之间的衔接,装备PS与PL之间的接口作业等;然后将硬件渠道的数据导入SDK,由软件工程师完结配套的的驱动和运用程序的开发。可见,传统的规划流程,需求许多团队和资源的介入,不简略。

而假如完结了上述规划作业之后,发现体系架构还需求优化,这就悲催了——规划不得不从头调整软硬件分区,上述整个开发流程又要从头进行一遍,并且许多情况下需求屡次迭代才干找到那个令人满意的体系架构和计划。由此消耗的时刻和资源,是巨大的,乃至是不可控的。

图2,传统的FPGA SoC运用开发流程(图片来历:赛灵思)

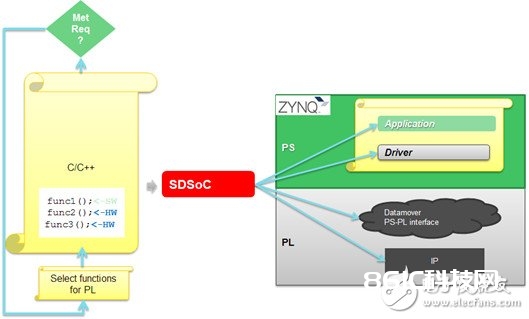

而运用SDSoC之后,许多作业是由东西主动完结的:省去了比如软件驱动和硬件衔接等繁复的手动作业,一起运用C/C++终端运用可以像函数调用相同输入调用用户算法IP;只需求单次点击,就可以完结分区设置以确认需求在可编程逻辑中运转的功用。

图3,运用SDSoC简化后的FPGA SoC运用开发流程(图片来历:赛灵思)

做一个不是非常精确的比方:SDSoC与传统东西和开发流程的不同,就像是主动挡与手动挡轿车的不同,它让杂乱的作业对用户变得“通明”,让用户实践的“操作”变得更简略,而用户由此被解放出来的精力,则可以用到考虑“要去哪儿、怎么走”等更高档的问题,而不是和“油离合作”较劲儿。

类比到FPGA SoC的运用开发中,用户最重视的部分往往是算法的终究完结和算法模块的优化——包含IP或是软件功用块——SDSoC的规划理念正是让用户可以愈加专心于这些核心问题,其他问题SDSoC帮你搞掂。从这个意义上看,SDSoC在“简略”的背面的确不简略。