在开发PL时一般都会用到分频或倍频,对晶振发生的时钟进行分频或倍频处理,发生体系时钟和复位信号,这是同步时序电路的要害,这时就需求运用到时钟导游IP,下面就介绍一下在vivado中进行PL开发时调用IP的办法。

首要翻开vivado,新建一个RTL项目。

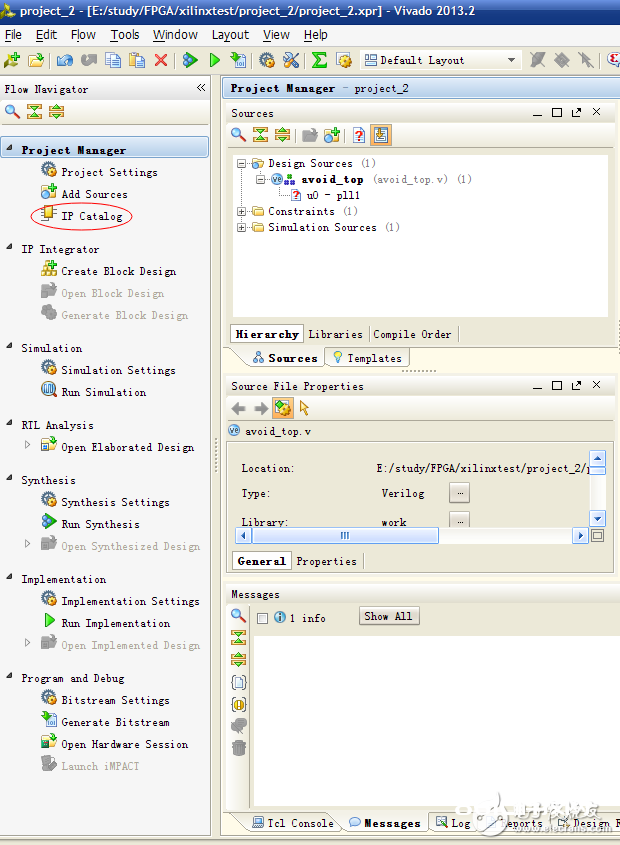

点击导航窗口上的IP Catalog 选项,如图一所示:

图一

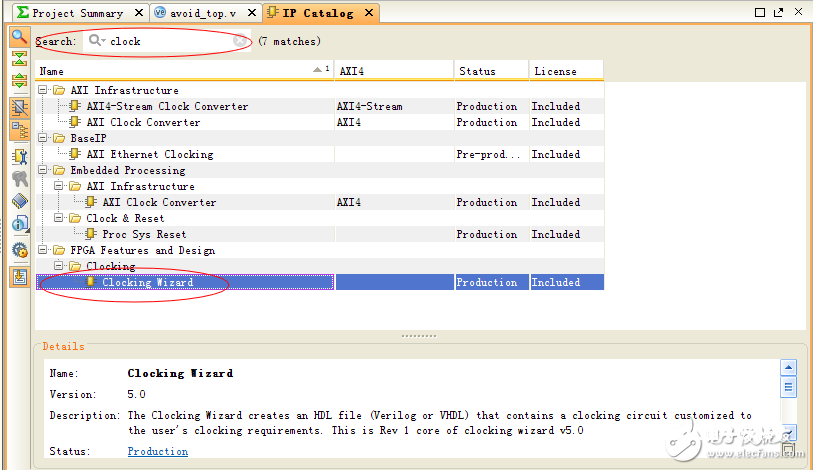

在search处查找自己想要的IP核的姓名,例如输入clock就会找到Clocking Wizard 这个IP核,如图二所示:

图二

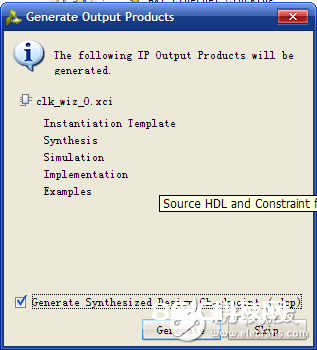

双击Clocking Wizard 这个IP核,就能弹出装备窗口,按自己的需求装备好IP核后,点击ok,会呈现下面的窗口,如图三所示:

图三

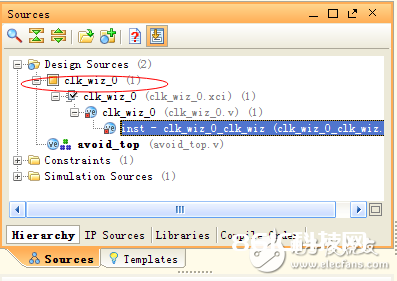

点击Generate,生成IP核,然后在source窗口就会呈现一个文件,如下图4所示:

图四

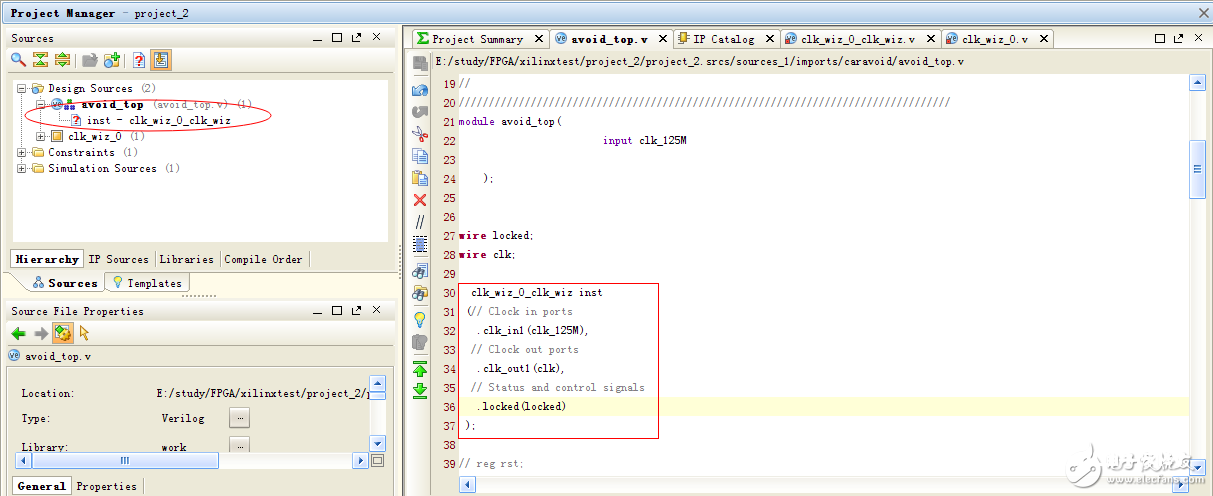

然后我就依照一般的写verilog的办法对这个IP进行例化,便是翻开clk_wiz_0.v文件,将里边的端口界说复制到顶层文件傍边,然后进行例化,可是这样做一直会报错,在顶层文件中不能辨认这个IP,如下图五所示,留意下图赤色符号部分,照理说是正确例化了,可是顶层文件那儿一直是问号。

图五

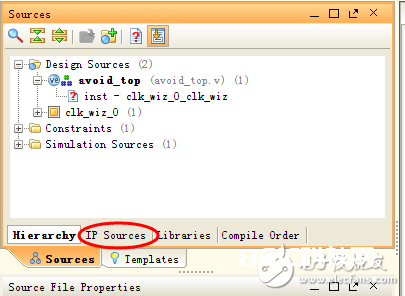

然后我又从头生成了一次IP核,仍是不可,通过查阅材料,我总算找到了正确的例化办法,在生成IP核后,在source窗口的下方会呈现一个IP source的标签,如下图六所示:

图六

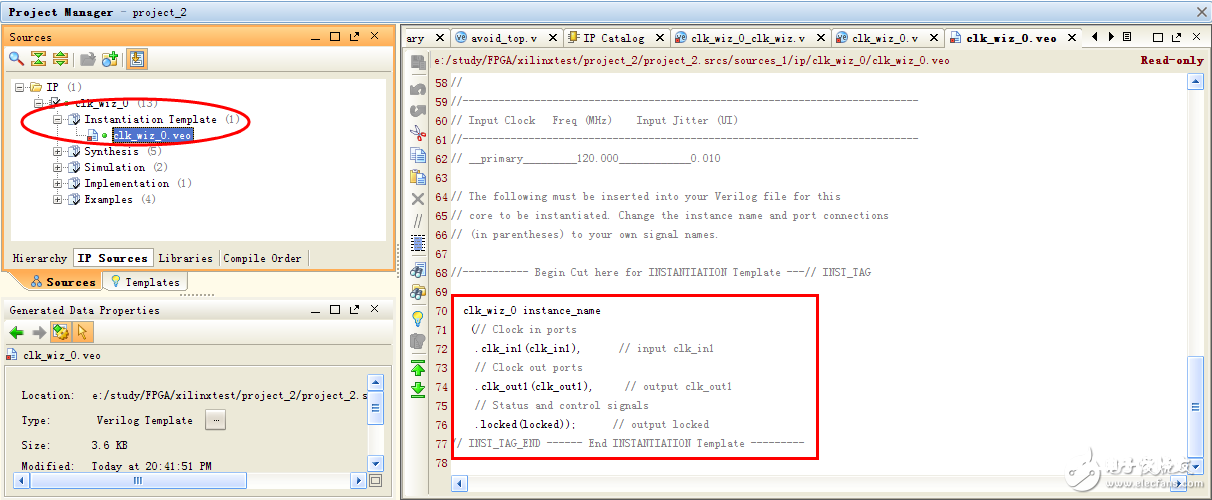

点击这个标签,然后你就会发现你生成的IP核,翻开它,然后翻开InstantiaTIon Template,你会发现一个*.veo文件,双击翻开它,把里边的没被注释的程序复制到顶层文件中,如图七所示:

图七

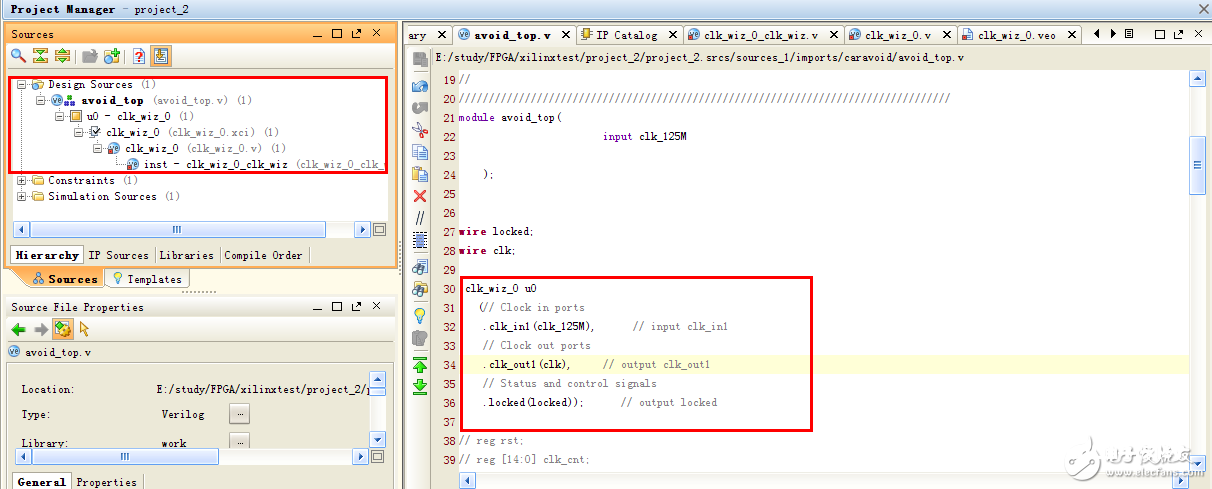

保存好顶层文件后,你会发现,咱们生成的IP核就成了顶层文件的下级文件了,问号也就消失了,IP核成功增加,如图八所示:

图八