前 言

所谓数字存储就是在示波器中以数字编码的方法来贮存信号,数字存储示波器的简称是DSO(“Digital Storage Oscilloscope”)。在DSO中,输入信号的波形先经A/D改换器将其模仿波形转化成了数字信号,然后存储在RAM中,需求时将RAM中存储的内容调出,经过D/A改换器,将数字信号康复为模仿量,显现在示波器的屏幕上。在数字存储示波器中,信号的处理功用和其显现功用是彻底分隔的,咱们在示波器上看到的波形是由收集到的数据经过重构后得到的波形,而不是加到输入端上信号的波形。

体系规划方案

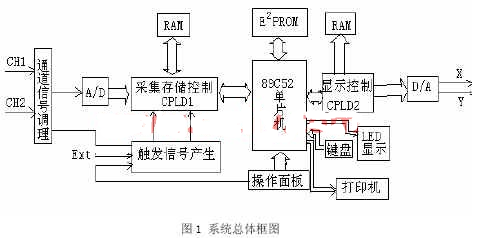

本体系选用单片机和可编程器件作为数据处理及操控中心,整个体系包含通道信号调度、触发信号发生、收集存储、数据交融处理、显现、操作面板、掉电维护等功用模块。图1给出了该体系的整体框图。

一、通道输入信号调度电路

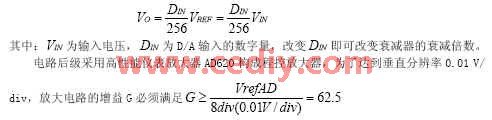

考虑到输入信号的动态规模较大,故本规划选用了先衰减后扩大的电路结构,电路前级选用8位双D/A TLC7528构成程控衰减器,将输入信号作为参阅电压,此刻D/A 的输出电压为

二、双限窗口比较器

双限窗口比较器用于起伏轴笔直灵敏度主动操控时的超限信号的检测。当通道调度电路输出的信号电压超出窗口规模时,比较器输出高电平,电路如图2所示。

图2 双限窗口比较器

三、操控面板电路

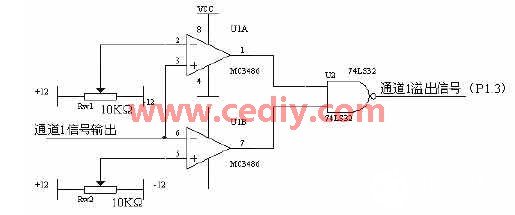

体系操控面板除键盘外,还设有通道1笔直方位、通道2笔直方位、触发电平、触发方位、主时基方位共5个调理旋钮,操作简单易行。单片机经过A/D合作多路开关来收集面板的操控数据,其电路原理图如图3所示。

图3 数据收集通道

图中,4051为八选一模仿开关,TLC0820为八位并行A/D,P1.2、P1.3、P1.4用来操控收集哪一个电位器的数据。

四、触发信号发生电路

触发电路的效果是终究发生一致的上升沿有用的触发信号。

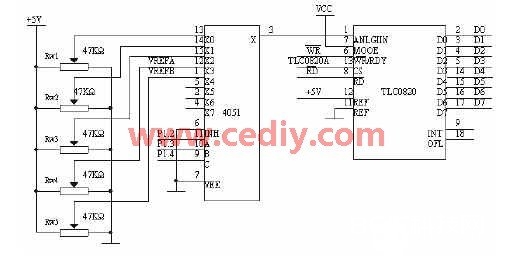

1、边缘触发信号发生电路:中心是比较电路。比较器选用MC3486,该芯片可处理10 MHz的输入信号,输出同TTL电平兼容。

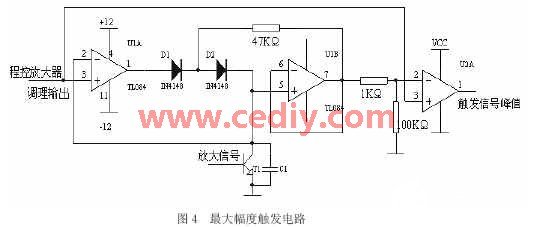

2、最大起伏触发发生电路:经过峰值坚持电路记载信号的峰值,并与输入信号进行比较,当输入信号起伏低于峰值坚持电路的输出电平常,比较器输出上升沿触发信号。电路原理如图4所示,图中的晶体管T1起取样坚持开关效果。

五、收集存储逻辑电路

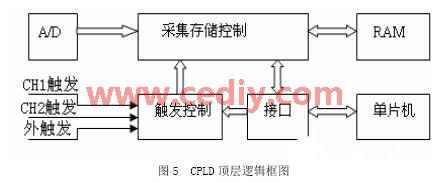

收集存储逻辑电路的效果是将A/D改换后的通道数据写入存储器中,其操控逻辑包含接口、触发操控模块、收集存储操控模块,由一片CPLD器材EPM7128SLC84来完结。图5给出了CPLD顶层逻辑框图。

其间,触发操控逻辑电路由触发挑选逻辑和触发使能逻辑组成。在单片机的操控下,触发操控逻辑电路与触发信号发生电路相合作,能够完结触发源挑选、触发方法挑选、触发条件挑选、触发电平调理等触发功用。收集存储操控模块为操控中心,主要由可编程分频器、地址计数器、推迟计数器和时钟挑选器四部分组成。

⑴可编程分频器:它的效果是供给采样时钟,其分频比由单片机依据采样率核算得出,然后转化为对应的操控字置入。

⑵地址计数器以及RAM、ADC的操控逻辑电路:收集时,地址计数器在采样时钟的同步下计数,为存储器供给地址,一起采样时钟也作为ADC芯片的读信号和RAM的写信号。计数器输出的最低位作为2个ADC芯片的挑选信号。这样,2个通道的数据别离存入奇地址和偶地址。

⑶推迟计数器:用于决议触发点的方位。经过设定触发方位,能够调查触发点前或触发点后或前后各一段时间内的波形。推迟计数器的初始值由单片机预先置入。改动推迟计数器的初始值,就改动了触发点的方位。

⑷时钟挑选器:收集时,挑选器选通采样时钟,地址计数器在采样时钟的同步下计数;收集完毕后,挑选器则选通单片机的读信号,单片机检测到收集完毕信号(由推迟计数器的溢出信号发生),便开端回读数据,每读一次数据,地址计数器就加1,因为计数器是循环计数,所以只需顺次读数,便能够读出一切的收集数据。

六、显现操控模块

显现选用示波器的X—Y方法。在X—Y方法下,示波器的笔直轴与水平轴的偏转电压均由外部供给。屏幕上每一个方位都对应一个X—Y坐标。因而,只需供给波形的坐标数据,经D/A转化送至X、Y轴即可。

显现操控电路由时钟挑选器、地址计数器及X、Y数据锁存器构成。在单片机写数据期间,时钟挑选器将写信号选通,作为地址计数器的时钟,存储数据的规则为Y1、X1、Y2、X2。在答应显现期间,时钟挑选器选通显现时钟,此刻,地址计数器以固定的频率循环计数,RAM的读信号直接用显现时钟充任,用地址作为X、Y锁存器的选通信号,让奇、偶地址的数据别离锁存到X、Y轴DAC的数据线上,发生对应的X、Y轴偏转电压。

体系软件规划

体系主程序流程图如图6所示。其间,初始化模块除包含一般的仓库指针、位标志等内容外,还能将保存在E2PROM中的参数调入体系。在是否答应收集模块中,要对各种条件进行判别,首要有必要在运转(RUN)状况下,如果是在中止(STOP)状况则一概不使能。其次,依据不同的触发方法,如在单次触发方法下,则有必要有单次开释标志才答应使能,而在主动和常态触发方法下则有必要在一个主循环完毕后才答应触发。

图6 主程序流程图

完毕语

在本规划中,可编程逻辑器材CPLD完结收集、存储和显现操控逻辑等功用,而单片机完结人机界面、体系操控、信号剖析、处理和改换功用。本规划的立异点在于除了具有单次触发存储显现功用外,还能对被测信号进行收集、存储和接连显现。

责任编辑:gt