作者 / 田元锁 赵润年 我国电子科技集团公司第四十一研讨所(安徽 蚌埠 233010)

*基金项目:我国电科技能创新项目《微波毫米波大带宽大规模MIMO测验技能研讨》

田元锁,1983年6月出世,工学硕士,工程师,首要研讨方向为电子测验与仪器开发、中频电路规划等。

摘要:移动通讯技能飞速发展,体系带宽不断添加,本文提出了大带宽矢量信号剖析仪的中频处理规划,用于处理大带宽矢量信号中频处理的难点,适用于多种矢量信号规范,能接纳高达100 MHz宽带的矢量信号,解调剖析功能的EVM值小于1%,满意大带宽矢量信号剖析的要求。

0 导言

IQ正交调制技能遍及使用于现代数字通讯体系,其调制信号能够用IQ两路来表明。作为调制信号,其信号质量必需求抵达要求,一般衡量把这种IQ正交调制信号当作一个矢量来剖析,映射到星座(Constellation)的I轴(横轴)Q轴(纵轴)上,分别对IQ两路信号进行剖析,也能够针对IQ信号衍生出来的多个目标进行剖析,如EVM,从不同的视点衡量了矢量调制信号的信号质量[1-7]。

现在通讯体系的信号变得越来越杂乱,如大的带宽、杂乱的调制办法,要求矢量信号剖析仪具有剖析大带宽、多种调试制式信号的剖析才能。因而在大带宽矢量信号剖析仪的规划,就必须满意以上要求。一般来说,矢量信号剖析带宽越大,数字下变频处理越杂乱,国外优异的矢量信号剖析仪表厂商一般选用大规模集成电路,手法先进,咱们学习其经历,并考虑本钱等要素,选用多片通用高速现场可编程逻辑器件来构成数字下变频器 [8-11]。

1 中频处理单元

1.1 数字下变频器的规划

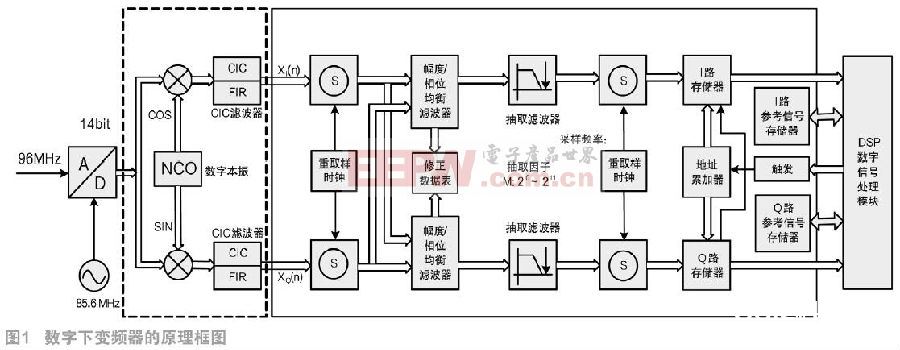

数字下变频器的功能对整个中频处理影响很大,首要要素有两个:一是表明数字本振、输入信号以及混频乘法运算的样本数值的有限长所引起的差错,即数字混频器和数字本振的数据位数不行宽,产生尾数切断;二是数字本振相位的分辨率不行而引起数字本振样本数值的近似取值。依据切断和近似的程度,会或多或少地影响数字下变频的功能[12-14]。依据上述的特色,高采样率数字下变频器的规划有相当大的难度,图1是数字下变频器的原理框图。

其间包括数字混频器、数字操控振荡器和低通滤波器三个部分。

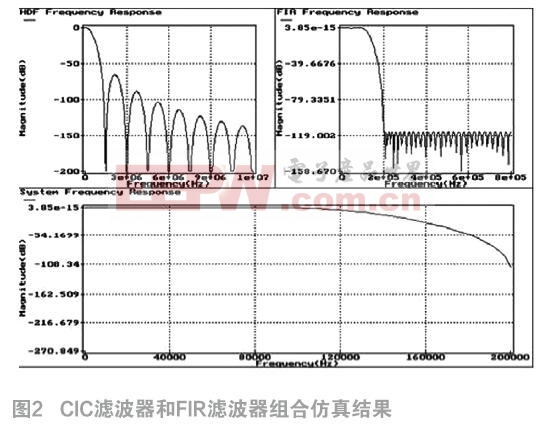

决议数字下变功能的最首要要素是数字操控振荡器(NCO),其效果便是产生一个抱负的正弦和余弦波。在信号采样率很低的时分,通过实时核算的办法产生。在信号采样频率很高情况下,实时核算的办法是不可能完结的,因而,最有用、最简洁的手法是查表法,即事前依据各个NCO正弦波相位核算好相位的正弦值,以相位视点作为地址存储该相位的正弦值数据,相位视点与该相位的正弦值一一对应,在每呈现一次信号采样值时,NCO就添加一个2π(fLO/fs),然后以相应相位累加视点作为地址,查看该地址上的数值并输出到数字乘法器。数字低通滤波器拟选用CIC滤波器和FIR滤波器相结合的办法,CIC滤波器占用资源少,并完结信号的抽取,FIR滤波器能够得到较好的带外按捺[12-14]。图2是CIC滤波器和FIR滤波器组合的一种仿真成果。

1.2 中频主动增益操控

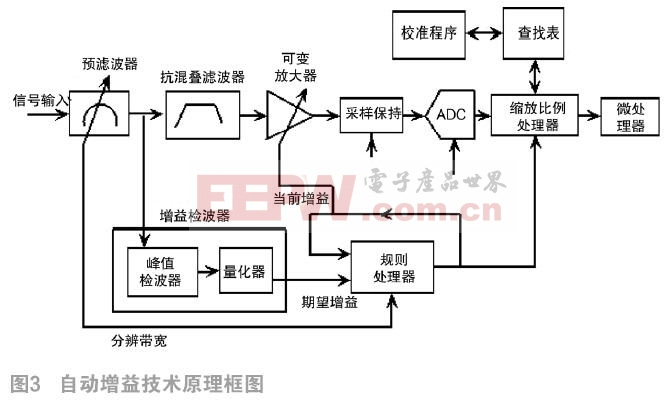

主动增益操控模块首要是运用主动量程改换技能,如图3所示,中心思维是运用通路中抗混叠滤波器有较长的延时特性,在ADC之前加一个可变增益调节器,在扫描过程中,使电路能进行充沛的峰值预检测和增益判别,然后调整进入ADC的信号增益。主动量程改换机制相当于扩展了ADC的量程规模,然后进步了丈量动态规模。图3中,可变带通预滤波器对中频信号进行预滤波。中频信号经预滤波后分为两路:主路信号进行抗混叠滤波,旁路信号进入峰值处理器。抗混叠滤波器存在很大的延时,它把输入信号延时到ADC采样时钟周期的很多倍。正是该延时的存在能够确保信号抵达ADC之前能够及时对输入信号进行电平判别处理和增益调整。滤波器的延时答应该技能在一个时钟周期内及时检测信号电平,然后鄙人一个时钟周期内决议需求调整的放大器增益而且完结电路设置。调整后具有最佳增益的信号抵达ADC,使动态规模最大化。特别是对那些需求更大动态规模的包括大、小信号的丈量时,动态规模现已通过加在ADC前面的增益改进了。增益规矩处理器依据峰值处理器的输出成果操控可变放大器的增益:输入为大信号,放大器增益减小;输入为小信号,放大器增益增大。别的增益规矩处理器还操控ADC量化数据的缩放处理,意图是去掉可变放大器的增益,康复本来信号起伏值。此外,通过提早对信号起伏检测和调整,能够避免信号过载然后维护ADC。

1.3 矢量调制差错的精细批改技能

矢量调制差错的精细补偿批改技能要处理两方面的问题:一是要减小I/Q驱动电路自身的频率响应、直流偏移等问题,尽量下降I/Q驱动电路对调制信号的影响;二是对驱动信号进行必要的批改,进一步进步调制信号的质量。

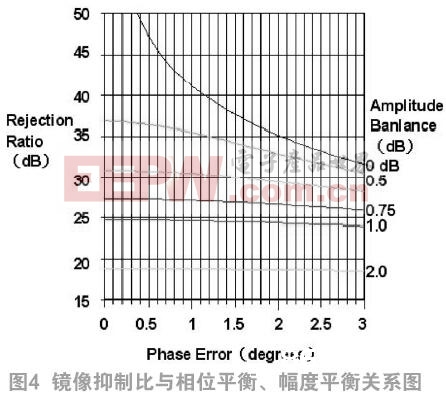

图4给出了镜像按捺比与相位平衡、起伏平衡之间的联系图。要抵达咱们规划要求,镜像按捺比要求在40dB以上。

首要,为了补偿基带通路中的损耗,改进调制频响,咱们规划了折线补偿计划改进通道的频率响应。

其次,任何元器件都不可能是抱负的,I和Q两路基带信号的增益不免会有细小的不同,矢量调制器也有功分两路功率不平衡、混频器变频损耗不一样等问题,终究体现为矢量调制信号的I/Q起伏不平衡,下降矢量调制信号的质量。

从图4能够看出,起伏平衡要求低于0.05dB,相位差错要求小于0.5度。明显,要抵达如此高的要求,不通过精细的补偿批改是不可能的。

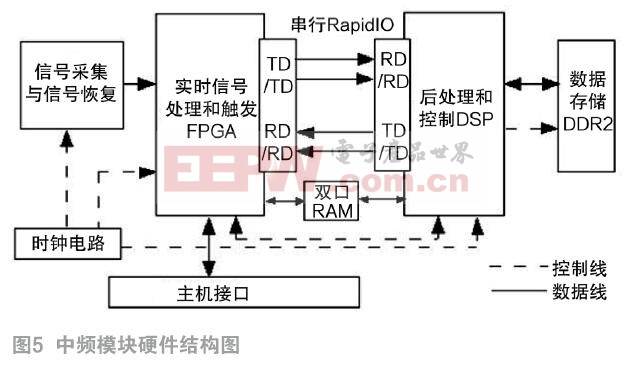

1.4 中频模块硬件规划

基带信号处理单元首要完结对信号进行实时信号剖析与实时信号产生等功能。图5为160MHz中频数字化处理剖析模块的硬件结构示意图。首要规划思维如下:采样频率为320MHz的ADC及时钟等外围电路构成了信号收集和调度电路。FPGA首要担任与主机接口衔接,操控数据收集,抽取滤波,实时FFT以及触发操控等处理,然后将时域数据通过串行RapidIO实时传输给DSP。DSP完结相应的时频域剖析处理,再把数据存入DDR2存储器中。DSP一起在主机操控下将频谱数据通过双口RAM回传给主机,一起也通过串行RapidIO将频率模板数据传输给FPGA,进行实时触发。

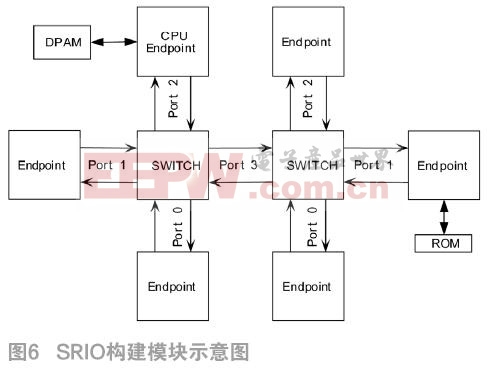

1.5 RapidIO规划

为了完结FPGA与DSP大数据量的交互,选用串行RapidIO规划。串行RapidIO是物理层选用串行差分模拟信号传输的RapidIO规范。SRIO 1.x 规范支撑的信号速率为1.25GHz、2.5GHz、3.125GHz; RapidIO 2.0规范将支撑5GHz和6.25GHz[15]。如图6所示,SRIO网络环绕两个根本模块构建而成:端点和交换机。端点对包进行源端(source)和宿端(sink)处理,而交换机在端口间传送包,对其不加解析。以3.125Gbps运转的4通道SRIO链路能够供给10Gbps的流量,且确保数据完整性。因为SRIO类似于微处理器总线,因而包处理是通过硬件完结的,这意味着可大起伏消减I/O处理方面的额定开支,下降推迟并添加体系带宽,但与大都总线不同,SRIO接口的引脚较少,带宽在链路为3.125Gbps的基础上可持续扩展。

2 相关试验成果

为了满意大带宽矢量信号剖析仪的要求,数据传输测验模块基带运用1x协议形式与4x协议形式,其接口时序图如图7、图8所示。

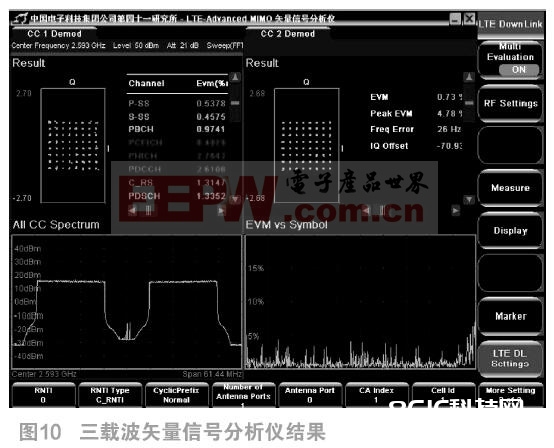

分别用两载波带宽为40MHz和三载波带宽为60MHz进行测验,其测验成果为图9和图10所示。

3 定论

通过相关测验,完结了大带宽矢量信号剖析仪的中频处理,得到了实践使用.选用该计划,信号剖析带宽可到100M,现在5G现已进入到咱们的日子,后续支撑5G的信号剖析是个难点,一起对中频提出了应战。

参考文献:

[1]刘青松,刘亮,范吉伟,王令.基波变频技能在频率合成器中的使用研讨[J] 国外电子丈量技能,2016, 35(5):66.

[2]胡炎.依据FPGA+DSP的数字中频收发机的规划[J] 现代电子技能,2016, 39(15):78.

[3]刘军军. 矢量调制信号差错剖析技能研讨 [D]. 哈尔滨工业大学. 2015.

[4]梁婷婷. 宽带矢量信号剖析技能研讨与完结[D]. 哈尔滨工业大学. 2015.

[5]李海虎,张超.依据FPGA的GHz宽带中频数字收集体系的规划[J] 国外电子丈量技能,2016, 35(4):55.

[6]管金新. 依据OFDM调制技能的中频数字收发信机规划与完结[D].南京航天航空大学. 2017.

[7]李敬,顾军,李晓惠.矢量网络剖析仪中频收集处理规划与完结[J] 国外电子丈量技能,2016, 35(5):79.

[8]赵润年,汤瑞.一种矢量信号解谐和频谱剖析的射频接纳通道规划[J] 国外电子丈量技能,2018, 37(4):50.

[9]刘琳琳.动态信号剖析仪的软件开发及完结 [D] 电子科技大学.2016

[10]阎啸.宽带多制式无线通讯信号解调测验算法研讨[D] 电子科技大学. 2010

[11]王宇扬. 数字通讯信号调制辨认与参数估计 [D]. 南京理工大学. 2014

[12]何水艳.浅析数字下变频中的NCO[J] 高级函授学报(自然科学版),2004, 17(1):53.

[13]闵紫辰.双向卫星时刻传递调制解调器的研讨[D] 西安电子科技大学.2005.

[14]崔斌斌.中频数字接纳机的规划与完结 [D].哈尔滨工业大学.2007.

[15]Navneet Rao.运用串行RapidIO衔接功能增强DSP协处理才能 [J] 电子规划使用,2007, 12:16.

本文来源于《电子产品世界》2018年第10期第32页,欢迎您写论文时引证,并注明出处。