推出新款处理器的时分,制造商们总喜爱叙述“更小的纳米制程工艺”、“更强壮的功能”、以及“更优异的能效体现”等概念。不过,很多人或许难以了解,为安在做得更小、功耗更低的一起,其功能反而还能够愈加强壮呢?有鉴于此,外媒PhoneArena特别撰写了一篇文章,为咱们解说与“制程”相关的的一些问题。

首要,什么是纳米?

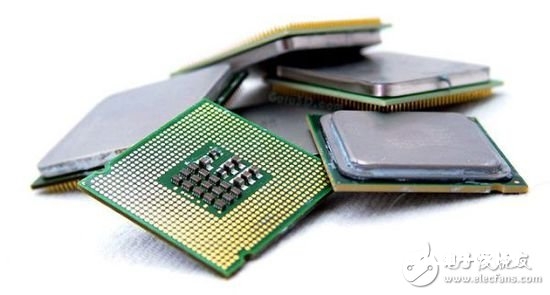

从本质上来说,一颗微处理器便是由选用不同资料制成的许多“层”堆叠起来的电路,里边包含了晶体管、电阻器、以及电容器等细小元件。

不过它们与被你扔进垃圾堆的大块头所选用的惯例元器件很是不同,因为它们的尺度现已小得肉眼难以看清,而规划更是能够让你感到震动。

在这些由元器件组成的“大军方阵”中,组件间的间隔通常用毫微米进行衡量。假如觉得“十亿分之一米”的概念不好记,那你也能够用“纳米”(nanometers)来描绘它。

最终,间隔越小,能够排布在芯片上的元器件就能够更多。

其次,为什么制程更小更节能?

答案是:减缩元器件之间的间隔之后,晶体管之间的电容也会更低,然后提高它们的开关频率。

因为晶体管在切换电子信号时的动态功率耗费与%&&&&&%成正比,因而它们才能够在速度更快的一起,到达愈加省电。

别的,这些更小的晶体管只需求更低的导通电压,而动态功耗又与电压的平方成反比(能效又提高)。

最终,推进半导体制造商向更小的工艺尺度进发的最大动力,便是本钱的下降。组件越小,同一片晶圆可切开出来的芯片就能够更多。

即便更小的工艺需求更贵重的设备,其出资本钱也能够被更多的晶片所抵消。

最终一点,为何制程工艺的腾跃简直都是每2年一次?

有利也有弊,在制程更小更省电的一起,晶体管的电流也更易走漏——即便其处于“封闭”状况。如此一来,又会导致芯片“更费电”。

在抱负国际中,这些%&&&&&%方阵会是彻底安稳的。而跟着电子设备变得越来越小,动摇、突变和分散都会对其形成很大的影响。

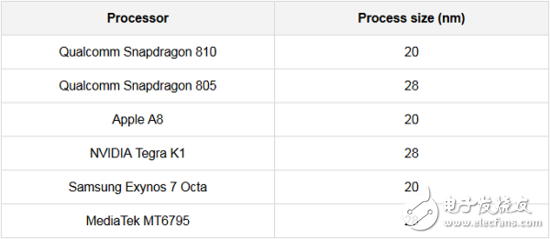

那么,如安在“制程”与“安稳”之间到达平衡呢?上方的表格就列明了当时市面上能够到达的移动芯片的“极限”。

当然,制造商们关于“极限”的追求是永无止境的。或许在不远的将来,咱们就能迎来量产版的“单原子巨细”工艺制程的芯片了。