0 导言

视频图形阵列显现接口是微机体系运用的一种通用显现接口,广泛运用于智能操控体系中,作为体系的显现终端。关于由嵌入式微处理器构成的图画处理体系来说,选用VGA显现输出具有兼容性强、显现内容丰富的优势。一起,VGA显现接口具有结构简略、功能牢靠、兼容性强、时序简略操控的特色。因而,结合FPGA的 VGA图画操控器在嵌入式的图画处理体系中有广泛的运用远景。

现在大多数计算机与外部显现设备之间都是经过模仿VGA接口衔接,计算机内部以数字方法生成的显现图画信息,被显卡中的数字/模仿转化器转变为R、G、B三原色信号和行场同步信号,信号经过电缆传输到显现设备中。

1 VGA显现

常见的VGA接口的五颜六色显现器,一般由cRT(阴极射线管)构成,色彩由R、G、B(红:Red,绿:Green,蓝:Blue三基色组成。显现选用逐行扫描的方法进行,即当扫描完一行时,再进行下一行的扫描,直到最终一行扫描完停止。VGA接口为显现器供给两类信号,一类是数据信号,一类是操控信号。

数据信号包括红、绿、蓝信号,简称RGB信号。操控信号包括水平同步信号(HSYNC)和笔直同步信号(VsYNc)。向显现器输出不同的分辨率时,水平同步信号和笔直同步信号的频率也不同。可是水平同步信号和笔直同步信号时序剖析相同,在扫描时均需求经过同步信号、同步后信号、行同步信号、同步后信号四个时段。仅以水平同步信号为例,其结构如图1所示。

VGA接口的显现器原理其实就相当于点阵,经过操控器的操控,点亮地点的行和列。所以水平同步信号是针对列像素而言的,而笔直同步信号是针对行像素而言的。

以显现800×600的图片巨细为例,依据VGA的时序规范,挑选6hz的改写频率。水平同步信号的同步信号包括128个列像素,同步后沿信号为 88个列像素,同步前沿信号为40个列像素,而屏幕显现部分为800个列像素,所以总共需求1 28+88+40+800=1 056个列像素。场同步信号的同步信号包括4个行像素,同步后沿信号包括23个行像素,同步前沿信号包括1个行像素,而屏幕显现部分为600个行像素,所以总共需求4+23+l+600=628个行像素,由此,液晶显现器显现一幅800×600的图画,需求的队伍像素别离为1056和628。

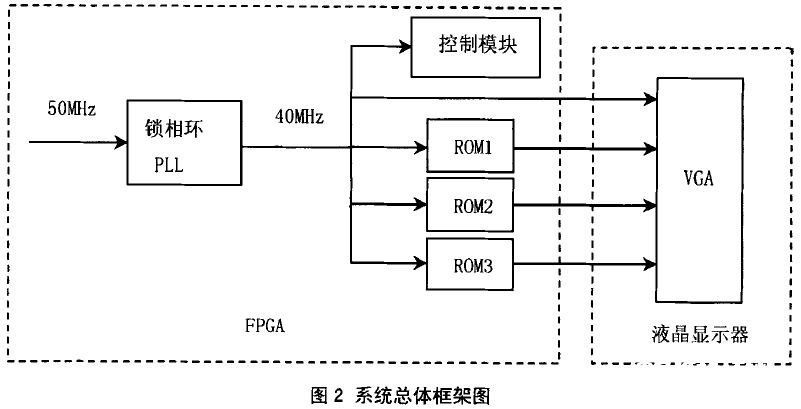

2 体系整体结构规划

本体系以FPGA EP2C8Q208C8为中心芯片,经过对VGA接口的操控,完成五颜六色图画的显现,体系结构框图如图2所示。

2.1锁相环PLL

锁相环路是一种反应操控电路,简称锁相环(PLL),一种输出必定频率信号的振动电路,也称为相位同步环(回路)。该回路运用使外部施加的基准信号与PLL 回路内的振动器输出的相位差安稳的反应操控来发生振动信号。在网络范畴中,PLL用于从接纳的信号中别离出时钟信号,能够经过实践电路或软件的方法完成。

因为FPGA的体系时钟为50MHz,而操控VGA的时钟为40MHz,所以在对VGA接口的操控时需求进行时钟转化,一般能够经过分频或者是调用 IP核的方法完成转化,可是因为经过自己写的分频程序假设在数据上处理不得当,简略发生毛刺,而调用quanersII软件自带的PLL内核,不只能够做到与体系时钟同相,并且时钟安稳,能够完成对VGA时序的严格操控,与硬件电路来完成锁相环比较,调用PLJ。内核不只能够做到操作简略,并且也节省了规划本钱。

2.2存储模块ROM

只读存储(Read一0nly Memory,ROM)是一种只能读出事前所存数据的固态半导体存储器圈。在体系框图中的三个ROM均用来存储色彩信息,因为本规划中运用图片的巨细为 128×128,即总共有128×128=16384个像素点,所以ROM的巨细设置为16384。这儿经过quanerII软件调用FPGA的ROM内核,将MATLAB提取的红、绿、蓝三基色数据经quanusII软件的处理,别离存入FPGA的ROMl、ROM2、ROM3中。在操控模块中写入 ROM的地址,在分频后的时钟操控下,将数据读到vGA的RGB三个引脚,完成液晶显现器的图片显现。

2.3 MATLAB的数据提取

MATLAB 作为强壮的数据处理东西,其根本数据单位是矩阵,它的指令表达式与数学工程中常用的表达形式十分相似,故用MATLAB来解算问题要比用 c,FORTRAN等言语简捷得多。在新的版别中也加入了对C,FORTRAN,C++,JAVA的支撑,能够直接调用,用户也能够将自己编写的实用程序导人MATIAB函数库中便利自己今后调用,此外许多的MATLAB爱好者都编写了一些经典的程序,用户能够直接进行下载就能够用,十分的便利。

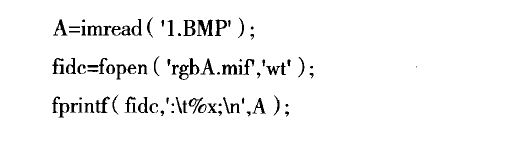

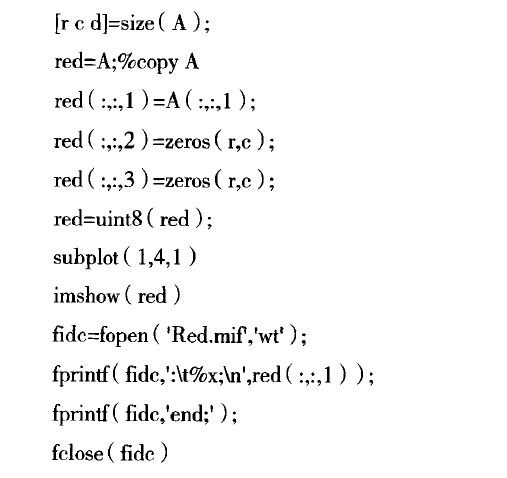

因为MATLAB软件中默许的图片格局为.JPc和.BNP,因而在运用MATLAB前需将原始图片经过Photo sh叩软件进行格局转化,转化后保存图片为.BMP格局,在弹出的位宽挑选对话框挑选24位,,然后再经过MATLAB提取红基色数据,程序如下所示,成果被保存在Red.mif文件里:

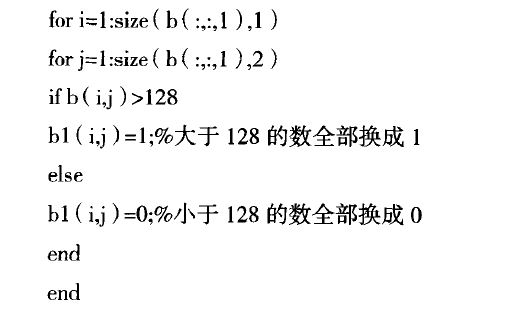

因为本规划所运用的VGA是三位的数据接口,因而蓝基色和绿基色数据也按照此方法提取。Red.mif中的数据是24位的,所以还需求对提取到的红基色数据进行转化。在MATLAB中做如下判别将24位数据转化为3位数据。

3 成果剖析

图画的显现如图3所示,显现成果表明,因为原图画是24位,即224种色彩,而FPGA操控的VGA只要3位即23种色彩,比较之下,以24位的图画作为规范,VGA显现的3位图画有显着失真的现象。

假如期望显现的图画愈加明晰,那么需求将vGA的显现接口从头作出电路修正,这样才干到达明晰显现的作用。

4 结束语

在许多图画处理体系中,需求将经过处理的图画显现出来,假如选用传统的方法将图画数据传回电脑并经过显现器显现出来,那么在传输的过程中就需求嵌入式体系的 CPU不断的对所传输的图画数据信号进行操控,这样就造成了CPU资源的糟蹋,相同体系还需求依托电脑,降低了体系的灵活性。假如选用FPGA对显现器的 VGA接口进行规划,数据流只需求在整个体系的内部活动,而不需求依托计算机,完成了体系的最小化,大大减少了电路板的尺度,增强了体系的牢靠性和规划的灵活性。

VGA接口相同也是LCD液晶显现设备的规范接口,经过VGA操控LCD能够使整个体系变得细巧,携带便利,使得运用的规模大大扩展。作者地点的全景视觉图象处理项目中,正是需求把经过处理的图画实时地直接地显现出来,放下对计算机的需求,以满意各种不同运用环境的需求。

经过FPGA对VGA接口的操控,不只完成了FPGA对任一图画的显现,并且其内部时钟可调性为规划带来了很大的便利,节省了硬件本钱。此计划能够广泛运用于数字视频体系、高分辨率的五颜六色图片图画处理、视频信号再现等各种范畴。

作者黄文杰,李灿平,丁然