什么是FPGA?

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器材的基础上进一步开展的产品。它是作为专用集成电路(ASIC)领域中的一种半定制电路而呈现的,既处理了定制电路的缺乏,又克服了原有可编程器材门电路数有限的缺陷。

FPGA的作业原理:

FPGA选用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包含可装备逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。 现场可编程门阵列(FPGA)是可编程器材,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器材)比较,FPGA具有不同的结构。FPGA运用小型查找表(16&TImes;1RAM)来完成组合逻辑,每个查找表衔接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可完成组合逻辑功用又可完成时序逻辑功用的根本逻辑单元模块,这些模块间运用金属连线相互衔接或衔接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来完成的,存储在存储器单元中的值决议了逻辑单元的逻辑功用以及各模块之间或模块与I/O间的联接办法,并终究决议了FPGA所能完成的功用,FPGA答应无限次的编程。

什么是ASIC?

现在,在集成电路界ASIC被认为是一种为专门意图而规划的集成电路。是指应特定用户要求和特定电子体系的需求而规划、制造的集成电路。ASIC的特色是面向特定用户的需求,ASIC在批量出产时与通用集成电路比较具有体积更小、功耗更低、可靠性进步、功用进步、保密性增强、本钱下降一级长处。

ASIC作业原理:

ASIC的规划办法和手法阅历了几十年的开展演化,从开端的全手艺规划开展到现在先进的能够全自动完成的进程。这也是近几十年来科学技术,尤其是电子信息技术开展的成果。从规划手法演化的进程区分,规划手法阅历了手艺规划、核算机辅助规划(ICCAD)、电子规划自动化EDA、电子体系规划自动化ESDA以及用户现场可编程器阶段。集成电路制造在只要几百微米厚的原形硅片上,每个硅片能够包容数百乃至不计其数个管芯。集成电路中的晶体管和连线视其杂乱程度能够由许多层构成,现在最杂乱的工艺大约由6层坐落硅片内部的分散层或离子注入层,以及6层坐落硅片外表的连线层组成。就规划办法而言,规划%&&&&&%的办法能够分为全定制、半定制和可编程IC规划三种办法。

怎样给他们适配供电体系(包含GPU):

在 FPGA、GPU 或 ASIC 操控的体系板上,仅有为数不多的几种电源办理相关的规划应战,可是由于需求重复调试,所以这类应战或许使体系的推出时刻严峻滞后。不过,假如特定规划或相似规划现已得到电源产品供货商以及 FPGA、GPU 和 ASIC 制造商的验证,就能够避免许多电源和 DC/DC 调理问题。剖析和处理问题的担负常常落在体系规划师的肩上。装备规划方案杂乱的数字部分现已占有了这些规划师的大部分精力。因而处理规划方案的模仿和电源部分就成了首要应战,由于电源并非如许多规划师所预期的那样是个简略的使命。

周全的电源办理从一开端就很有应战性

一切规划使命一开端都很有应战性,例如为一个包含收发器、内存模块、传感器、线路衔接器以及网状 PCB 走线和多层 PCB 平面的杂乱体系规划电源办理方案。不过,乱七八糟地运用 DC/DC 稳压器、电容器、电感器、散热器和其他散热办法以及组件布局来应对电源办理规划或许会导致后续规划问题。假如体系规划师匆忙决议挑选较差的处理方案,那么后来或许呈现调试作业进行不下去的状况。

从哪里开端电源办理规划

以一种体系化和考虑周全的规划办法,能够很有掌握地开端任何电源办理电路的规划。换句话说,在 PCB 拼装之前,假如剖析是精确的,处理了电源办理相关的规划应战,那么就能够简化电源办理电路的规划。别的,电源办理攻略给出的电路通过测验和验证,满意 FPGA、AS%&&&&&%、GPU 和微处理器以及选用这些及其他数字组件的体系之要求。运用通过验证的电源办理处理方案规划电源办理电路,将保证项目从一开端就很有掌握。这是让规划方案从原型阶段快速进入出产阶段的要害,由于这样能够节约电源调试时刻。

一个很好的比如:给 Arria 10 FPGA 和 Arria 10 SoC 供电

体系开发人员能够运用 FPGA 开发东西评价 FPGA,而无须规划一个完好的体系。图 1 和图 2 显现了 Altera 公司新的 20nm Arria 10 FPGA 和 Arria 10 SoC (片上体系) 开发电路板。这些电路板通过 Altera 公司的测验和验证,罗列了有关布局、信号完好性和电源办理的最佳规划实践。

面向内核、体系和 I/O 的电源办理。面向 Arria 10 等高端 FPGA 的电源办理处理方案应该慎重挑选。

一个通过精心方案的电源办理规划能够减小 PCB 尺度、减轻分量并下降杂乱性,一起下降功耗和冷却本钱。这对优化体系功用而言是必不可少的。

例如,为图 1 中 Arria 10 GX FPGA 的内核供电的 12V DC/DC 稳压器供给 0.95V/105A,该 DC/DC 稳压器有几个特色,对 SoC 的省电办法起到了弥补效果:

·Arria 10 的 SmartVID 运用 DC/DC 稳压器中集成的 6 位并联 VID 接口来操控 DC/DC 稳压器,在静态和动态状况下下降了 FPGA 功耗。

·DC/DC 稳压器运用 DCR 值十分低的电流检测办法,通过最大极限下降电感器中的功耗,进步了功率。温度补偿在电感器温度较高时坚持精确度或 DCR 值不变。

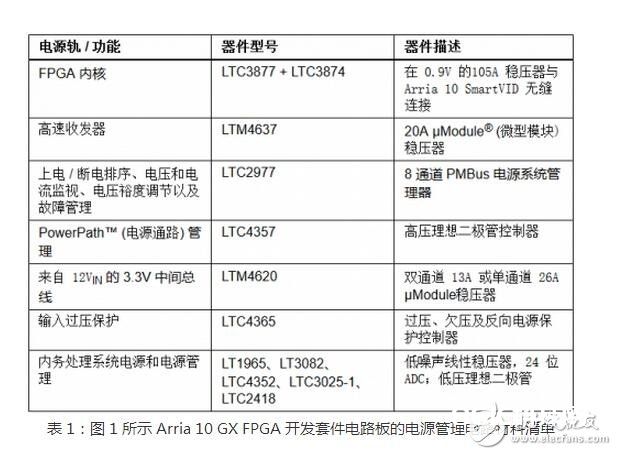

表 1 概述了图 1 所示 Arria 10 开发套件电路板的电源轨和功用。该表列出了凌力尔特公司的器材,并描绘了每种器材的功用。拜访 www.linear.com.cn/altera,点击 Arria,了解本文所示两种电路板的详细技术信息。

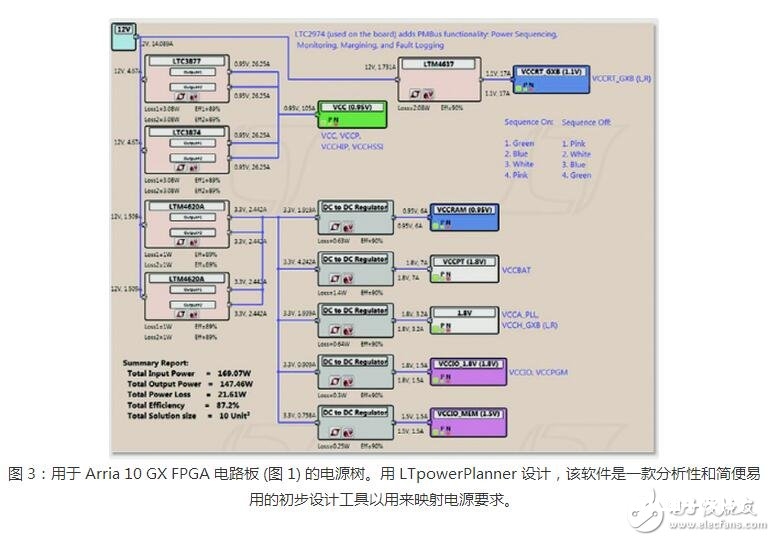

用 LTpowerPlanner 规划东西定制电源树

假如开发套件中罗列的规划不能满意自己的电源要求怎么办?在这种状况下,能够用根据 PC 的 LTpowerPlanner® 东西来完成体系电源树的个性化和优化。

从开发套件中给出的主张着手;然后容易地重新组织电源构件、改动电源额定值、核算功率和功耗、仿真每个电源构件、挑选 DC/DC 稳压器器材类型并验证定制处理方案。

LTpowerPlanner 用来发生满意 Arria 10 开发套件中 FPGA 要求及体系要求的电源树 (图 3),是用处更广泛的 LTpowerCAD® 规划东西之一。

LTC2974 (用在电路板上) 添加 PMBus 功用:电源排序、监督、裕度调理和毛病记载

Loss:功耗

Sequence On:排序接通

Sequence Off:排序断开

Green:绿色

Blue:蓝色

White:白色

Pink:粉色

DC to DC Regulator:DC 至 DC 稳压器

Summary Report:总结报告

Total Input Power:总输入功率

Total Output Power:总输出功率

Total Power Loss:总功耗

Total Efficiency:总功率

Total SoluTIon Size:处理方案整体尺度

LTpowerCAD 可协助用户:

·挑选详细的凌力尔特 DC/DC 稳压器,以与给定电源功用标准匹配

·挑选适宜的电源组件 (例如: 电感器、电阻器和%&&&&&%器)

·优化功率和功耗

·优化稳压器环路稳定性、输出阻抗和负载瞬态呼应

·将规划方案输出到 LTspice®

定论

咱们能够有掌握地开端电源办理电路布局。运用 LTPowerCAD 和 LTPowerPlanner 这类东西,能够大大简化对负载点稳压器以及各部分剖析成果的映射使命。为了举例说明这些优势,本文选用了用于 Altera Arria 10 FPGA 和 SoC以及其他 Altera FPGA (包含电源树和资料清单) 的开发套件规划攻略。拜访以下网址可获得有关信息:www.linear.com.cn/altera。如需了解赛灵思 FPGA 开发套件,请拜访:www.linear.com.cn/xilinx。这些开发套件均通过Altera 、赛灵思或第三方开发商的测验和验证。