高速串行互连是标志并行数据总线向串行总线改变的技能里程碑,这种技能是削减规划师面临的信号堵塞问题的办法。这种改变是由业界对体系本钱和体系扩展才能的要求所推进的。跟着芯片技能的开展和芯片尺度的缩小,用速率达数千兆位的高速串行互连来替代传统的并行结构变得简单易行。

技能开展

低压差分信号技能(LVDS) 是隐含在许多高速串行互联规范界说后边的中心电子信号技能。当数据率高于3Gbps时,电流形式逻辑 (CML) 和低压正射极耦合逻辑(LVPECL) 是关键技能。

功耗和数据率是取舍各种信号技能办法的关键因素。

为进一步下降信令引脚的数量和信号布线的长度,然后下降电路板的规划杂乱程度,时钟被嵌入到了数据中。在接纳端,需求对时钟数据进行康复,这种办法现已开展老练并被许多串行通讯体系所广泛选用。

此外,为提高抗噪才能和共模按捺才能,LVDS信号技能大多选用沟通耦合。这就需求直流平衡线路编码计划并保持有满足的切换用于时钟康复。咱们选用IBM开发的8b/10b编码计划或相似的计划,将8位字转化成10位的符号并终究用于传输。8b/10b编码还包含用于同步的特别操控字符(被称为“K字符”) 。

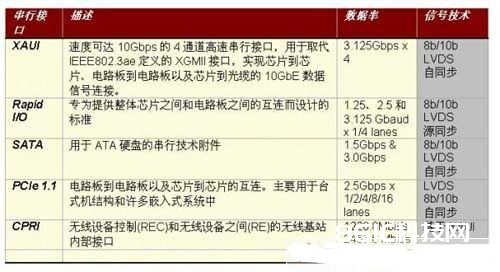

高速串行接口一般用于各种芯片之间的接口、背板的互连以及设备与设备的衔接。以下是被广泛选用的一些串行互连协议:

芯片到芯片/背板串行互连:

XAUI

Rapid I/O

SATA

PCIe

CPRI (操控规划和基站间的3G通讯协议)

硬件机箱设备与设备的串行电缆接口:

HDMI, DVI, 显现端口

USB

1394

高速串行协议开发的开展敏捷,完成牢靠规划解决计划成为规划师面临的应战,因而一种能便利进行规划变化、测验和调试的渠道能有用协助客户验证规划以及尽快将产品投放市场。Xilinx的Virtex系列FPGA 带有嵌入式RocketIO收发器硬内核,然后具有了这种灵活性。这种器材在一片器材中集成了最多24个RocketIO,能完成内部通道绑定的多通道办法,也能够完成去失真。

运用Rocket I/O内核在信号强度、信号预加剧/去加剧和数控阻抗方面的可编程性,很简单完成不同的I/O规范。运用FPGA来完成还能够在FPGA结构内部很快完成规范协议。高速接口意味着器材内有很多需求处理的数据,而在FPGA内部很简单完成并行处理结构。咱们信任,因为FPGA的本钱现已开端下降且FPGA关于不断开展的串行协议规范有更杰出的适应性,将有越来越多运用选用FPGA而不是ASSP来进行接口规范的处理。

好像高速网络交流和选用多处理器结构的超级计算机相同,在多FPGA的规划中千兆位收发器的选用是必定的。带有RocketIO收发器的FPGA会成为衔接处理器矩阵和FPGA的仅有互连挑选,以保证整个板上处理器矩阵间的数据吞吐才能。

当完成高速串行衔接时,不可避免地会碰到传输线的影响和信号完好性问题。这些都是高速互连规划中有必要当心处理的难题。

时钟源时钟颤动

串行数据颤动:

总颤动

随机颤动

确定性颤动

信号调度特性

电缆和PCB布线中的介质损耗

预加剧和去加剧驱动器(频率挑选性放大器和衰减器)

均衡(无源和有源均衡)

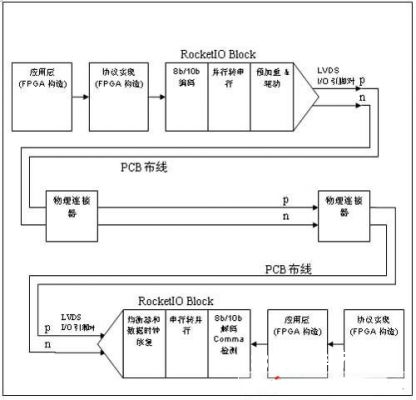

下面是一个通用数千兆位串行互连的完成框图及相关要求。

调试东西

要供给一个完好牢靠的解决计划,在规划调试方面的专业经历和功率都至关重要。规划人员一般需求留意板级的信号完好性,这也往往是简单出现问题的当地。千兆位规划需求专门的设备来捕获板上的高速串行信号。所以在进行电路板规划时预留的一些便利信号探针附着的测验点,以保证被测验单元在考虑负载和被施加搅扰时能实在捕获信号。

要剖析速度高达3Ghz (例如PCIe,XAUI等)的串行协议,需求采样速度20 Gs /秒以上的6Gh或更高速的数字信号剖析设备。这种规模的仪器一般能剖析和生成眼图(Eye-Diagram)、误码率“澡盆”(bathtub)曲线图、进行颤动剖析和捕获各种跃迁瞬间。

咱们运用FPGA这类可编程器材的优点之一(因为其可编程才能)是能够用它来发生测验信号并能象信号剖析器相同来捕获和剖析片上的信号。这就能断开板级信号通路进行链路功能测验。Xilinx的Chipscope Pro SerialIO 东西套件中现已包含了IBERT(内部误码率测验)。这就象嵌入在FPGA中的一种高速串行数据剖析数字示波器。这种十分有用的办法很便利在信号的端点进行板级信号完好性剖析。

至于在Xilinx FPGA结构内完成的运用规划,运用ChipScope Pro Analyzer东西能够持续进行可视化的规划模块调试。

高速千兆位互连必定会成为往后芯片间(chip-to-chip)、电路板间(board-to-board) 或设备间(box-to-box) 通讯的开展方向。缩短技能(Shrinking technology) 提高了数据处理的速度。更高的处理速度意味着大吞吐量数据设备需求读入多得多的数据而且会有巨量处理后的输出数据喷涌而出。一起,跟着芯片因工艺的提高而进一步缩小,在芯片中能有用地完成能够作为高速串行干线衔接网关的高速串行解串器(SERDEs)和驱动器。

差分信号技能会持续向驱动高达10Gbps及以上单线数据传输率的方向开展。芯片互连很快会替代并行接口,串行接口会成为遍及选用的芯片间接口。存储器(DRAM或SRAM) 将经过高速串行存储器接口来衔接。

在电路板规划和布局时,规划人员会优先考虑信号对的道路组织和怎么保证信号的完好性,而不是并行总线的布线方位分配。PCB板布局规划工程师有必要了解微波传输带和带状线的信号完好性以及怎么完成信号完好性的仿真。PCB板规划人员有必要具有高频或RF规划范畴的常识和特别技巧。

好像前期TTL向LVCMOS电平改变时的状况相同,或许会被制定一个商定的规范,以一致芯片间高速串行互连的规范。这很像开发一个板上的网络,在不同芯片中供给了一个即插即用的接口。这种办法的优点是能够选用更少引脚数的封装,然后减小封装尺度,下降封装本钱,终究下降器材本钱。

当一切这一切都被充沛界说和开发后,FPGA将成为快速验证、采用某种规范和将最新的串行互连协议出产化及实用化的可编程渠道。