数字逻辑已经成为当今全部电子电路的中心,无论是FPGA、微操控器、微处理器仍是分立逻辑。数字体系选用有必要互连在一起以履行所需功用的很多组件。保证此类数字体系正常运转的要素是完成全部数字组件之间通讯以及在其之间树立同步的时钟信号。因而,咱们一直需求一种源头来生成这种时钟信号。

信号源选用振动器的方式。尽管当今大多数微操控器具有集成RC振动器,可是这种内部RC振动器生成的时钟质量往往不足以支撑与体系中其它模块通讯所需求的精度。因而,需求选用可以为整个体系供给时钟信号而且满意对精度、信号完整性与稳定性等全部要求的外部振动器。

本文首要介绍在各种温度和时刻下生成精确时钟的振动器的不同方面。所包含的主题包含:

振动器 – 振动的根本规范

● 石英晶体振动器

● Q因子及其重要性

● 不同类型的晶体振动器

本文后续部分将包含规划而且供给有关以下方面的具体阐明:

● 皮尔斯晶体振动器(XO)

● 电压操控振动器(VCXO)

● 温度操控振动器(TCXO)

● 恒温振动器(OCXO)

● 负电阻的重要性

什么是振动器?

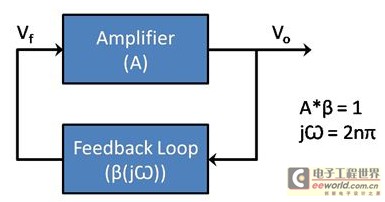

在电子学中,任何无需输入即可生成重复信号的电路都可以称为振动器。简而言之,振动器把DC能量转换成预期频率的AC能量。振动频率取决于规划振动器时所选用的元件的常数。振动器电路一般选用具有正反馈的放大器;为了坚持振动,电路有必要恪守巴克豪森规范;也就是说,闭环振动体系的增益有必要是整数,而环绕环路的相移有必要为2nπ,其间‘n’可所以任何整数,如图1所示。

图1:闭环振动体系

在开端鼓励时,电路中的仅有信号是噪声。因为正反馈机制,契合振动频率与相位条件的噪声重量会在体系中传达而且起伏不断增大。信号起伏不断增大,直到遭到有源元件本身内部特性或许外部自动增益操控(AGC)单元的约束。树立振动所需时刻取决于多种要素,如:噪声信号的起伏与环路的增益等等。

有各种振动器可以用于树立振动,如:RC振动器、LC振动器与石英振动器。可是,就必定温度与时刻规模内的精度与精确度而言,石英振动器是首选,因为其具有高Q(104 ~106规模内,相比之下LC为102,后文胪陈),这有助于在温度与时刻规模内到达更高的稳定性。

石英振动器

石英晶体振动器的最大卖点是可以在各种负载与温度条件下发生稳定频率。在石英晶体振动器中,当把电压源施加到晶体,其会发生机械摄动,然后发生特定频率(又称为共振频率)的电压信号。所发生的频率取决于晶体的形状与巨细,因而晶体在切开之后就不能再用于任何其它频率。晶体越薄,则共振频率越高。

晶振的等效电路:

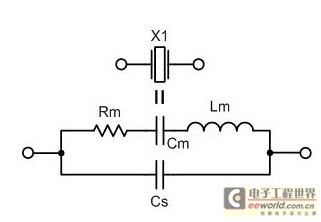

石英晶体可以建模为如图2所示的LCR电路。

图2:晶振的等效电路

其间,Lm、Cm与Rm分别是晶振的动生电感、动生电容与动生电阻,而Cs是晶振的电气衔接构成的分流电容。石英振动器以两个共振频率运转:Ls与Cs的串联共振构成的串联共振频率(fs)、Ls的并联共振以及Cs与Cp串联组合构成的并联共振频率(fp)。并联共振频率又称为操作基频。

图3:共振器电抗与频率

图3阐明晶振的电抗与频率曲线。在远离fp的频率时,晶振显现出电容性。在fs与fp之间的区域,其显现出电理性。fs与fp之间的区域是晶振的正常操作规模。振动器与稳定性:

对振动器而言,有许多要素影响到体系的频率稳定性,如:老化、噪声、温度、坚持电路、可坚持性、磁场、湿度、电源电压与轰动。下面介绍某些重要要素:

时刻形成的不稳定

时刻形成的不稳定可以分为两类 – 老化与短期的不稳定性。老化是因为振动器内部改动形成的频率的长时刻体系性改动。不过,尽管这种频率改动只要几PPM,可是其触及需求精确频率的体系时(如:DTV、机顶盒等)则至关重要。相反,短期的不稳定性本质上具有随机性,往往可以界说为噪声。

老化 – 有多重要素会形成老化,如:质量搬运、晶体遭到的应力、热膨胀、装置受力、键合单元、晶振的驱动电平以及DC偏置。

短期噪声 – 抱负振动器的输出是完美的正弦波。不过,在抱负体系中,随机噪声或闪耀噪声会导致信号的相位偏移,然后形成频率为了坚持2nπ相位条件而发生改动。相位斜率dφ/df与QL成正比,有必要坚持高值,以保证最高的频率稳定性。为了坚持高相位斜率,Cm 应当尽或许小。因而,fs与fp之间电抗/频率的斜率越大,则频率稳定性越高。

温度形成的不稳定

晶振的共振频率在室温下改动很小。可是,跟着升至极点温度,额定频率的改动开端增大,有或许到达几十ppm.

核算等运用可以承受这一点。可是关于导航、雷达、无线电通讯、卫星通讯等对精确度与精度要求极高的运用来说,则无法承受这种巨大改动。因而,此类运用需求在体系中添加额定的补偿元件(拜见下文)。

可调谐性形成的不稳定

使振动器在较宽的频率规模内具有可调谐性会导致不稳定性。为了完成可调谐性,需求选用滤波器消除剩余的频率形式。可是,这样会形成可调谐振动器很难完成更高的频率稳定性,因为负载电抗会遭到滤波器中运用的变抗器的杂散电容与电感的影响。

坚持电路形成的不稳定

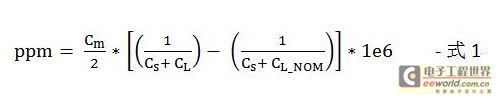

当在晶振中添加外部负载电容器时,电容器与杂散电容的容差会导致实践负载电容违背所需值。负载电容的这种改动也会形成频率改动。其可从下式求出:

其间,

Cm 是晶振数据表中指定的晶振动生电容;

CS 是晶振数据表中指定的晶振分流电容;

CL_NOM 是晶振数据表中指定的负载电容;

CL 是晶振端子之间的实践电容。

Q因子

Q因子可确认共振器贮存的能量(L与C贮存的能量)与丢失的能量(R中耗费的能量)之比。选用更高Q因子的部分优势如下:

● 选用更高Q因子可以下降相位噪声,因为相位噪声对晶振的Q因子有很强的依赖性。这样可以进步频率稳定性。

● 更高Q因子的另一个优势是缩小带宽。

● Q因子与从鼓励到衰减的时刻成正比。因而,Q因子越高,衰减时刻越长。衰减时刻与环路增益一起有助于缩短晶振的发动时刻。

晶体振动器的类型

依据用于完成更高精度与精确度的补偿办法,晶振可以分为四类。最常用的晶振包含:

● 无补偿晶体振动器 – XO

● 电压操控晶体振动器 – VCXO

● 温度操控晶体振动器 – TCXO

● 恒温振动器 – OCXO

补偿晶体振动器(XO)

如前所述,此类振动器随温度可呈现巨大改动 – 数量级到达±15ppm.关于不需求十分精确的时钟的运用而言,无补偿晶体振动器是不错的挑选。

电压操控晶体振动器(VCXO)

电压操控晶体振动器选用晶振十分根本的特性 – 即只要振动器端子的负载电容(CL)与一般称为CL_NOM的特定值(一般由晶振制造商供给)匹配时才以指定频率共振。例如,假如晶振标为25Mhz与14pF,其意味着只要振动器端子供给的CL为14pF时它才以25MHz进行差错为0PPM的共振。从式1可以看出CL增高可以下降频率的PPM差错。假如CL > CL_NOM,则ppm变成-ve,其意味着晶振将以低于中心频率的频率共振。而CL

晶体振动器的这种特性在VCXO中得以完成,其需求在十分小的规模内精确盯梢频率,比方用于数字机顶盒、DTV等。VCXO选用衔接到其输入端子的附加变容二极管(或许在振动器端子改动CL的任何其它手法,如:有时候选用数字操控的电容阵列)。此二极管以反向偏置形式衔接,而且在其之上施加外部电压。因为变容二极管的特性,其电容随施加的电压发生改动(即:随反向偏置电压的增高而下降),而振动器输入端的CL也相同如此。因而,咱们可以经过改动二极管上的电压来操控振动的频率而且对电路进行微调。在实践运用中,可以经过比照输出频率和预期频率而生成差错电压。

温度操控振动器(TCXO)

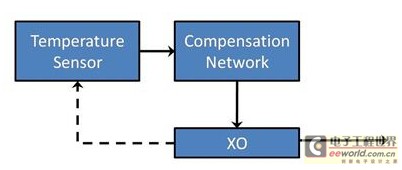

TCXO的作业原理与VCXO相同 – 当晶振串联电抗组件(%&&&&&%器或电感器)时可以改动振动的频率(拜见图3 -fs与fp之间的区域)。TCXO选用温度传感器丈量温度而且为变容二极管供给一个纠正信号,以补偿频率中的改动。

图4: TCXO的方框图

图4显现了TCXO的方框图。选用此办法可以到达0.1ppm的精度。

恒温振动器

在这种结构中,晶振和其它温度灵敏组件都放置于一个温度操控室(恒温箱),其调理到晶振的频率/温度斜率为0的温度。这样,振动器就可以在温度方面取得最高的稳定性,数量级可达0.001ppm.