现在一般盛行的做法都是用串行通讯的,那样能够节约I/O口的。可是有的时分在端口不紧缺的时分能够考虑用并行的方法来进行设置。

这个暑假我在进行电子比赛的培训,关于这个问题找到了一些相关的材料,能够供给一些协助。

假如是这方面的高手的话,其实会发现这个原理很简单,只需了解一些I/O口的设置就能完成了。可是假如关于单片机或许FPGA的I/O口的电路不了解的话或许就会走许多的傍门了。

闲话少说,进入正题。

首要,仍是要了解所谓的推挽输出与漏极输出两者的差异。先说说漏极开路(OD),它与集电极开路(OC)是共同的,便是把下图的三极管改成CMOS管便是了。

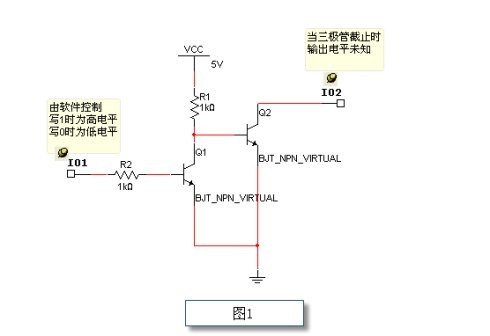

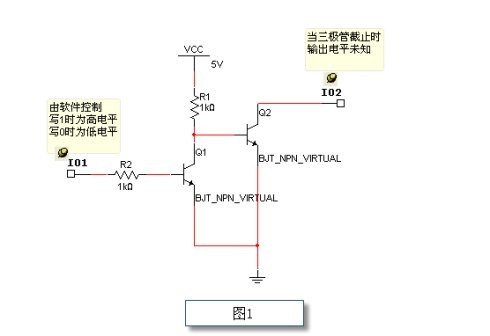

集电极开路(OC)输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左面的三极管为反相之用,使输入为“0”时,输出也为“0”)。关于图1,当左端的输入为“0”时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V电源经过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开封闭合);当左端的输入为“1”时,前面的三极管导通,然后边的三极管截止(相当于开关断开)。

为了便利了解,咱们把上面的图1改写成图2的姿态。

图2中的开关受软件操控,“1”时断开,“0”时闭合。很明显能够看出,当开封闭合时,输出直接接地,所以输出电平为0。而当开关断开时,则输出端悬空了,即高阻态。这时电平状况不知道,假如后边一个电阻负载(即便很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。也便是说这个输出端的电平是受负载的影响的。这样是很不安稳的,要防止这种状况。最多的便是运用上拉电阻。

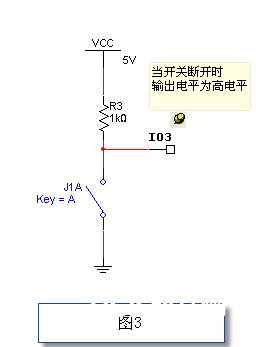

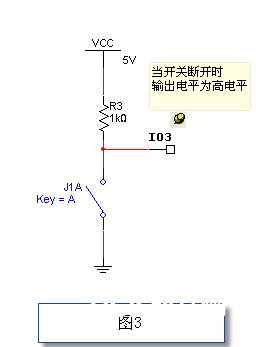

再看图三。图三中那个1K的电阻便是上拉电阻。假如开封闭合,则有电流从1K电阻及开关上流过,但由于开封闭和时电阻为0(便利咱们的评论,实践状况中开关电阻不为0,别的关于三极管还存在饱满压降),所以在开关上的电压为0,即输出电平为0。假如开关断开,则由于开关电阻为无穷大(同上,不考虑实践中的漏电流),所以流过的电流为0,因而在1K电阻上的压降也为0,所以输出端的电压便是5V了,这样就能输出高电平了。可是这个输出的内阻是比较大的(即1KΩ),假如接一个电阻为R的负载,经过火压核算,就能够算得最终的输出电压为5*R/(R+1000)伏,即5/(1+1000/R)伏。所以,假如要到达必定的电压的话,R就不能太小。假如R真的太小,而导致输出电压不行的话,那咱们只要经过减小那个1K的上拉电阻来添加驱动才能(所谓的驱动力,往往与电流有关的)。可是,上拉电阻又不能获得太小,由于当开封闭合时,将发生电流,由于开关能流过的电流是有限的,因而约束了上拉电阻的取值,别的还需要考虑到,当输出低电平时,负载或许还会给供给一部分电流从开关流过,因而要归纳这些电流考虑来挑选适宜的上拉电阻。

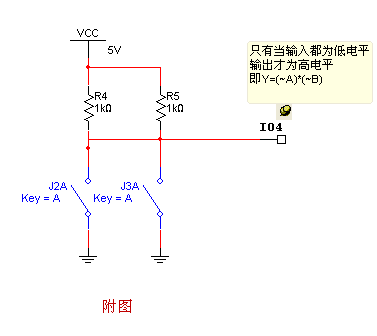

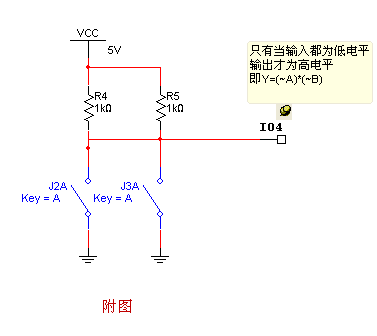

P.S:提到OC门的话,咱们都能想到三态门,那么就不得不提起它的“线与”功用了,这个功用是很便利的。操作上面也很简单。如下附图:

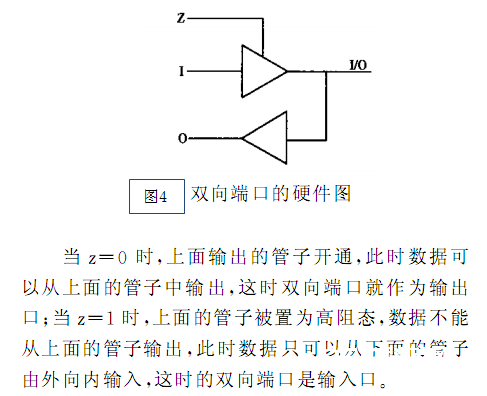

另一种输出结构是推挽输出。推挽输出的结构便是把上面的上拉电阻也换成一个开关,当要输出高电平时,上面的开关通,下面的开关断;而要输出低电平时,则刚好相反。比起OC或许OD来说,这样的推挽结构高、低电平驱动才能都很强。假如两个输出不同电平的输出口接在一同的话,就会发生很大的电流,有或许将输出口烧坏。而上面说的OC或OD输出则不会有这样的状况,由于上拉电阻供给的电流比较小。假如是推挽输出的要设置为高阻态时,则两个开关有必要一起断开(或许在输出口上运用一个传输门),这样可作为输入状况,有些单片机的一些IO口便是这种结构。

总结:从上面也能够知道了,I/0输出有两种方法。那么现在的难点便是怎样让I/0口输入数据。其实上面现已讲过了,便是只需要把输出设置为高阻状况就能够了。那么有些新人就会问了,都设成高阻状况了,数据还怎样输入啊?这其实是一个误区,其根本是没有了解I/O口的结构。

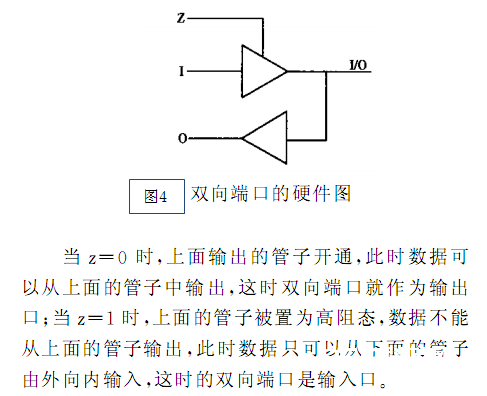

假如咱们将一个读数据用的输入端接在输出端(这便是上面疑问的答案了),这样便是一个IO口了(51的IO口便是这样的结构,其间P0口内部不带上拉,而其它三个口带内部上拉),如图4所示。当咱们要运用输入功用时,只需将输出口设置为1即可,也便是要把下面的z=1,这样就相当于那个开关断开,而关于P0口来说,便是高阻态了。

到现在为止,现已把输入输出端口原理现已批注了了。假如了解了上面所讲的,那么写程序也便是的把对应的端口进行设置就OK了,比较简单的。假如不明白,能够问我,QQ或许邮件都能够,最终我会留下联系方法的。

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/fangan/dianlu/258484.html