SPICE是一种查看电路潜在安稳性问题的有用东西 。本文将介绍一种运用SPICE东西来查看电路潜在安稳性的简略办法。

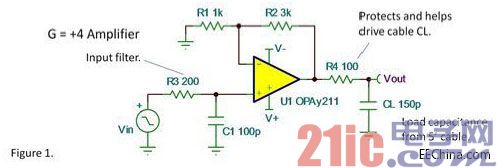

图1是运用OPA211 建立 的一个同相放大器,在许多运用中,仅仅对图1做了较小的变化。R3和C1构成了输入级滤波器。R4是电路的输出电阻,当运放输出级连接到其它外部电路时,R4起到维护效果。CL用来等效5英尺电缆。

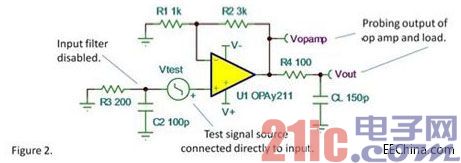

该电路的小信号阶跃呼应或许方波的呼应曲线是查看潜在安稳性问题的最方便和最简略的办法。图2是仿真电路。值得注意的是电路输入端连接到地,输入测验信号源直接连接到运放的同相输入端。输入级的滤波器将推迟输入信号的边缘。假如你想知道一个钟是怎么发生铃声的,你应该运用一个铁锤敲击它,而不是一个橡皮棒。

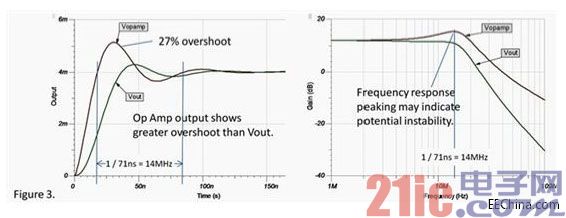

呼应曲线是在运放的输出端勘探,而不是电路的Vout节点。R4和CL构成了滤波器以至于Vout节点不能真实地显现出运放的过冲。为了查看安稳性,咱们需求知道运放是怎么作业的。

注意到输入信号的起伏是1mV(在运放输出端的起伏是4mV)。咱们期望得到小信号的呼应曲线。若输入信号是大信号,则会涉及到压摆率的问题,将减小过冲,不能真实地反响潜在的不安稳性。

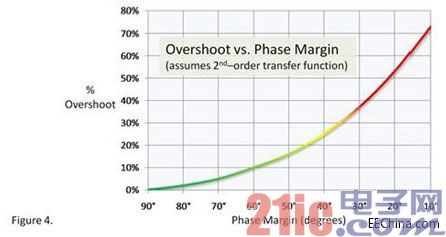

从仿真成果能够看出,在运放的输出端有挨近27%的过冲,较大的过冲会导致运放在任何条件下都是不安稳的。假定这是一个二阶安稳体系,它意味着挨近38度的相移裕量。别的,注意到频率呼应曲线中存在相当大的尖峰,这是另一个潜在的不安稳的痕迹。起伏峰值在14MHz时呈现,其正好是时域上振铃周期的倒数。普遍认为,当信号的过冲小于或等于20%时,相移裕量大于或等于45度,运放就能够视为安稳的。

有更多深层次的剖析能够经过SPICE仿真得到,例如:经过开环波特图找到相位裕量和增益。可是关于大多数简略的电路,上文说到的是指示潜在不安稳问题的非常好的办法。当然,任何SPICE仿真都取决于运放macro模型的准确性。现有的最优异的SPICE模型都不可能是完美的。此外,电路的差异性,非抱负的元部件,电路板布线带来的寄生参数,低质量的电源退耦,都能够影响电路的安稳性。这便是为什么你应该进行电路的仿真而且做实践的测验,比较两者之间的差异并进行优化。SPICE是一个很有价值且很有用的东西,可是不能彻底依托SPICE来检测电路的潜在安稳性,由于SP%&&&&&%E不能考虑到运放实践运用时的一些参数。