作者/ 马永旺1,2 何洋1,2 杜鹏程1,2 李振国1,2 胡毅1,2 唐晓柯1,2 1.北京智芯微电子科技有限公司 国家电网公司要点实验室 电力芯片规划剖析实验室(北京 100192) 2.北京智芯微电子科技有限公司 北京市电力高可靠性集成电路规划工程技能研究中心(北京100192)

摘要:金融双界面运用中,LDO(Low-dropout Regulator,低压差线性稳压器)为片内数字电路及首要模仿电路供给电源,高精度LDO能够确保数字电路及首要模仿电路作业状况及功耗安稳。为了进步金融双界面运用中LDO输出电压的精度,提出了一种LDO参阅电压上电切换电路。在高压电源下规划一个不精准的BG(Bandgap带隙基准)仅用于发动进程,规划一个高精度BG在LDO的输出电压下作业。上电时,LDO首要运用高压电源域下BG的参阅电压,确保整个发动进程顺利完结,一起关断POWER管,使低压作业下的电路不受上电过冲的影响,当LDO及高精度BG完结发动进程之后,将LDO的参阅电压切换至高精度BG。测验成果显现,LDO输出电压的随机失调有用减小,由传统结构的±7%左右下降到±3.69%,而且能够减小芯片面积。

导言

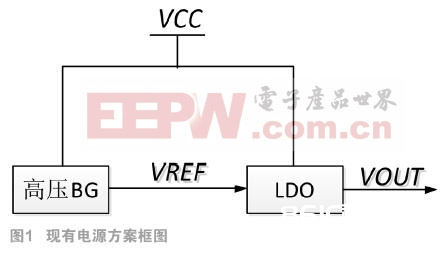

在金融双界面芯片的运用中,因为外部的触摸电压改变规模很广(1.62V~5.5V),所以需求运用低压差线性稳压器(LDO),用于将触摸电压进行稳压,以供给芯片内部的数字电路及低压模仿电路运用,LDO输出电压的精度直接遭到基准源发生的参阅电压精度影响。在传统完结方法(如图1所示)中,BG直接做在触摸电压下,因为触摸电压的改变规模比较广,所以BG需求运用高耐压晶体管(高压管)进行规划,高压管尽管耐压高,可是缺点也是很明显的,沟道长度较大,随机失配大,完结相同的精度时,高压管需求更大的面积及功耗。一起,运用高压管规划的BG发生的参阅电压具有很大的随机失调,所以也造成了终究LDO发生电源的差错规模很大。为了进步电源的精度,减小运用面积,期望能够将BG做在LDO的输出电压下。可是,BG为LDO供给参阅电压,而LDO又为BG供给电源,这样存在一个死循环。

本文提出的上电切换电路能够处理这一问题。在LDO内部有一个粗糙的基准源,能够在上电初始阶段,为LDO供给一个粗糙的基准,使得LDO发生电压,以供给给高精度BG运用,当高精度BG发动之后,会触发切换进程,将LDO所运用的参阅电压,由粗糙的基准源切换至高精度的基准源。

1 电路原理

因为在金融双界面运用中,LDO的输入电压改变规模很广(1.62V~5.5V),而且有可能上电速度十分快(最快可到达100ns);所以,假如上电就敞开LDO的功率管,会导致高压直接传递到LDO的输出,而使得LDO后边所接的低压MOS管击穿,导致电路失效。

1.1 现有技能剖析

现有技能如图1所示,BG的电源由触摸电压直接供给,这样BG会运用高压管进行规划,因而,VREF的随机失调会十分大,依据经历,大约会有±7%以上的随机失调。很显然,±7%的差错使得LDO输出电源VOUT十分不精确。为了减小面积并提高精度,提出了参阅电压上电切换的处理方法。

1.2 上电切换电路剖析

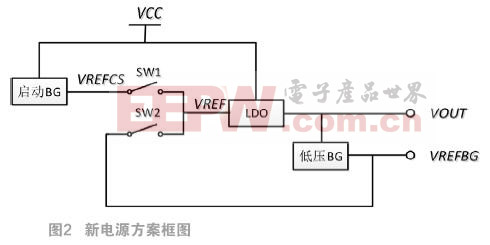

如图2所示,将低压BG做在LDO的输出电压VOUT下,这样就能够运用低压MOS管取得更小的面积以及更小的随机失调。

为处理上电时LDO没有输入参阅电压的问题,做了一个发动用的低精度BG,用于供给上电进程中LDO的参阅电压。

当VCC上电时,发动BG开端作业,LDO的POWER管初始被封闭,当发动BG发生的参阅电压及参阅电流供给给LDO之后,LDO开端发动;当VOUT电压升高到必定电压之后,会使得低压BG发动,发生VREFBG参阅电压;当LDO以及低压BG均完结发动进程,会触发SW1和SW2开关进行切换,将LDO运用的参阅电压由VREFCS切换成为VREFBG,然后取得高精度的VOUT电压。

2 晶体管级电路规划

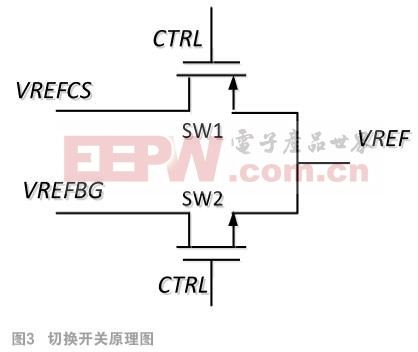

上电切换电路首要由两部分电路构成,分别为切换开关电路以及切换信号发生电路。

切换开关电路如图3所示。在上电切换之前,切换信号CTRL为低,将SW1导通,SW2断开,LDO运用发动BG发生的不精准的VREFCS参阅电压。当LDO以及低压BG完结发动进程之后,切换信号CTRL变为高电平,将SW2导通,而将SW1断开,LDO运用高精度的VREFBG电压。

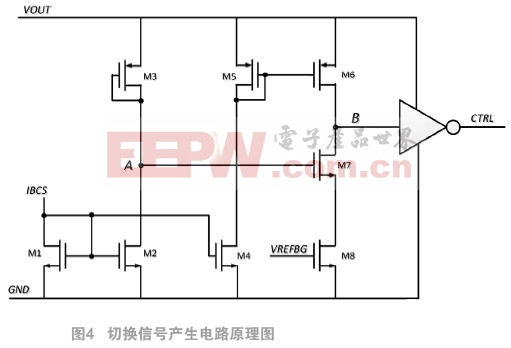

切换信号CTRL的发生电路如图4所示。M1、M2、 M4、M5和M6构成电流镜,将输入的参阅电流IBCS进行仿制。M3将PMOS管进行二极管衔接,A点电压VA与电源VOUT之间相差Vgsp;VA操控M7的栅极,当VA高于M7的阈值电压时,M7敞开;M8的栅极由VREFBG操控,当VREFBG高于M8的阈值电压时,M8管敞开。

作业进程如下:

上电后,当LDO发动,VOUT电压比较低时,此刻低压BG没有发动,VREFBG电压为低,M7和M8管关断,B点电压由M6管充电,然后VB为高,CTRL为低。当 VOUT持续上升到高于Vgs3+Vgs7时,M7管敞开;VOUT给低压BG供电,当低压BG发动,VREFBG升高,然后敞开M8管;所以,当一起满意两个条件:(1)VOUT高于Vgs3+Vgs7;(2)VREFBG高于Vgs8。M7和M8一起敞开,将B点拉低,然后导致CTRL的翻转,由低电平转换为高电平。

3 测验成果

电路在和舰 110nm CMOS工艺完结,发动BG和LDO总面积为364μmx334μm,静态电流为30μA;

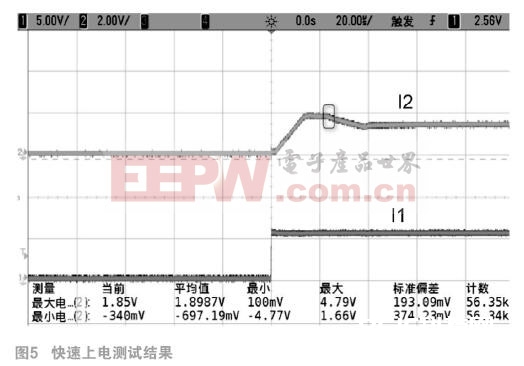

图5是常温以及高低温情况下,100ns快速上电的测验成果,其间l1为电源VCC,l2为LDO输出的VOUT电压。

在VCC快速上电时(100ns时刻内,由0V上升到5V),VOUT电压并没有过冲,而是缓慢上升,当VOUT到达必定高度,且低压BG完结发动之后,进行了参阅电压的切换进程(圈中所示的时刻点),此刻,LDO的参阅电压由低压BG发生的VREFBG供给,具有较高的精度。

由常温及高低温测验成果可知,该电路在按捺了快速上电进程中的过冲现象的一起,运用切换电路,发生了高精度的LDO输出电压。

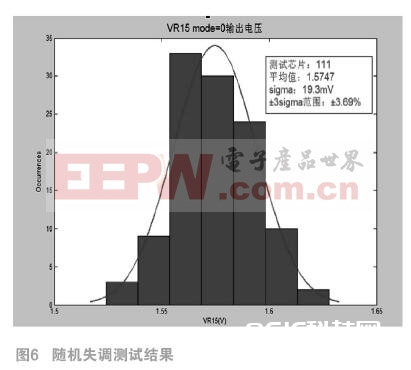

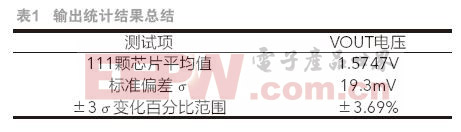

对111颗芯片进行电压测验,并进行了计算剖析,得出了LDO输出电压随机失调的成果,如图6所示。

将计算成果列表如表1所示。

能够看到,因为该电路运用低压BG为LDO供给参阅电压,所以VOUT电压的随机失调比较小,由传统结构的±7%左右下降到±3.69%,而且能够减小芯片面积。

4 定论

本文介绍了一种LDO参阅电压上电切换电路,剖析了现有技能的缺点以及处理计划,并详细剖析了晶体管级的电路完结,终究给出了测验成果。测验成果表明,本文所提出的参阅电压切换计划能够在快速上电时防止过冲的情况下,使LDO发生较高精度的输出电压,能够满意金融双界面运用的需求,并已成功运用在两颗金融双界面芯片中。

参阅文献:

[1]吴颖杰,周巍,于忠臣.高性能片内集成CMOS线性稳压器规划[J].电子%&&&&&%运用,2009(10):67-70.

[2]许长喜.低压低功耗CMOS带隙电压基准及发动电路规划[J].半导体学报, 2005, 26(10):2022-2027.

[3]PM Gray,RG Meyer.Analysis and design of analog integrated circuits. Fourth edition. John Wiley&sons, Inc, 2001.

[4]刘帘曦,杨银堂,朱樟明.根据MOSFET失配剖析的低压高精度CMOS带隙基准源[J].西安电子科技大学学报:自然科学版, 2005, 32(3):348-352.

[5] J Torres, M El-Nozahi, A Amer.Low Drop-Out Voltage Regulators: Capacitor-less Architecture Comparison[J].Circuits & Systems Magazine IEEE, 2014,14(2):6-26.

[6] Ka Nang Leung, Philip K. T. Mok.A Capacitor-Free CMOS Low-Dropout Regulator With Damping-Factor-Control Frequency Compensation[J].IEEE Journal of Solid-State Circuits,2003,38(10):1691-1702.

[7] Ka Nang Leung, Philip K. T. Mok.A CMOS voltage reference based on weightedV for CMOS low-dropout linear regulators[J].IEEE Journal of Solid-State Circuits, 2003, 38(1):146-150

[8]刘阳,李强,余昭杰,等.根据0.35μm CMOS的高性能LDO稳压器规划[J].吉林大学学报:信息科学版,2012,30(5):470-474.

[9] Qadeer Ahmad Khan, Sanjay Kumar Wadhwa, Kulbhushan Misri.Low power startup circuits for voltage and current reference with zero steady state current[J].International Symposium on Low Power Electronics & Design,2003:25–27.

本文来源于我国科技期刊《电子产品世界》2016年第11期第74页,欢迎您写论文时引证,并注明出处。