静电放电是CMOS电路中最为严峻的失效机理之一,严峻的会构成电路自我焚毁。论说了CMOS集成电路ESD维护的必要性,研讨了在CMOS电路中ESD维护结构的规划原理,剖析了该结构对地图的相关要求,要点评论了在I/O电路中ESD维护结构的规划要求。

1导言

静电放电会给电子器材带来破坏性的结果,它是构成集成电路失效的首要原因之一。跟着集成电路工艺不断发展,CMOS电路的特征尺度不断缩小,管子的栅氧厚度越来越薄,芯片的面积规划越来越大,MOS管能承受的电流和电压也越来越小,而外围的运用环境并未改动,因而要进一步优化电路的抗ESD功用,怎么使全芯片有用面积尽或许小、ESD功用牢靠性满意要求且不需求添加额定的工艺过程成为IC规划者首要考虑的问题。

2 ESD维护原理

ESD维护电路的规划意图便是要防止作业电路成为ESD的放电通路而遭到危害,确保在恣意两芯片引脚之间产生的ESD,都有合适的低阻旁路将ESD电流引进电源线。这个低阻旁路不光要能吸收ESD电流,还要能箝位作业电路的电压,防止作业电路由于电压过载而受损。在电路正常作业时,抗静电结构是不作业的,这使ESD维护电路还需求有很好的作业稳定性,能在ESD产生时快速呼应,在维护电路的一起,抗静电结构自身不能被损坏,抗静电结构的负效果(例如输入推迟)有必要在能够承受的范围内,并防止抗静电结构产生闩锁。

3 CMOS电路ESD维护结构的规划

大部分的ESD电流来自电路外部,因而ESD维护电路一般规划在PAD旁,I/O电路内部。典型的I/O电路由输出驱动和输入接纳器两部分组成。ESD 经过PAD导入芯片内部,因而I/O里一切与PAD直接相连的器材都需求树立与之平行的ESD低阻旁路,将ESD电流引进电压线,再由电压线散布到芯片各个管脚,下降ESD的影响。详细到I/O电路,便是与PAD相连的输出驱动和输入接纳器,有必要确保在ESD产生时,构成与维护电路并行的低阻通路,旁路 ESD电流,且能当即有用地箝位维护电路电压。而在这两部分正常作业时,不影响电路的正常作业。

常用的ESD维护器材有电阻、二极管、双极性晶体管、MOS管、可控硅等。由于MOS管与CMOS工艺兼容性好,因而常选用MOS管结构维护电路。

CMOS工艺条件下的NMOS管有一个横向寄生n-p-n(源极-p型衬底-漏极)晶体管,这个寄生的晶体管敞开时能吸收很多的电流。使用这一现象可在较小面积内规划出较高ESD耐压值的维护电路,其中最典型的器材结构便是栅极接地NMOS(GGNMOS,GateGroundedNMOS)。

在正常作业状况下,NMOS横向晶体管不会导通。当ESD产生时,漏极和衬底的耗尽区将产生雪崩,并伴跟着电子空穴对的产生。一部分产生的空穴被源极吸收,其他的流过衬底。由于衬底电阻Rsub的存在,使衬底电压进步。当衬底和源之间的PN结正偏时,电子就从源发射进入衬底。这些电子在源漏之间电场的效果下,被加快,产生电子、空穴的磕碰电离,然后构成更多的电子空穴对,使流过n-p-n晶体管的电流不断添加,最终使NMOS晶体管产生二次击穿,此刻的击穿不再可逆,则NMOS管损坏。

为了进一步下降输出驱动上NMOS在ESD时两头的电压,可在ESD维护器材与GGNMOS之间加一个电阻。这个电阻不能影响作业信号,因而不能太大。画地图时一般选用多晶硅(poly)电阻。

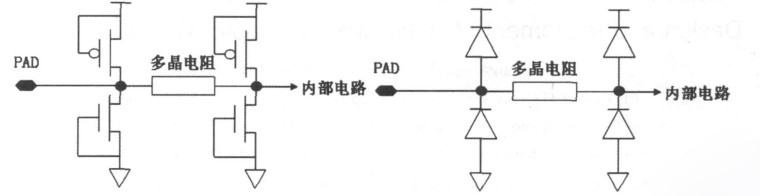

只选用一级ESD维护,在大ESD电流时,电路内部的管子仍是有或许被击穿。GGNMOS导通,由于ESD电流很大,衬底和金属连线上的电阻都不能疏忽,此刻GGNMOS并不能箝位住输入接纳端栅电压,由于让输入接纳端栅氧化硅层的电压到达击穿电压的是GGNMOS与输入接纳端衬底间的IR压降。为防止这种状况,可在输入接纳端邻近加一个小尺度GGNMOS进行二级ESD维护,用它来箝位输入接纳端栅电压,如图1所示。

图1常见ESD的维护结构和等效电路。

在画地图时,有必要留意将二级ESD维护电路紧靠输入接纳端,以减小输入接纳端与二级ESD维护电路之间衬底及其连线的电阻。为了在较小的面积内画出大尺度的NMOS管子,在地图中常把它画成手指型,画地图时应严厉遵从I/OESD的规划规矩。

假如PAD仅作为输出,维护电阻和栅短接地的NMOS就不需求了,其输出级大尺度的PMOS和NMOS器材自身便可充任ESD防护器材来用,一般输出级都有双维护环,这样能够防止产生闩锁。

在全芯片的ESD结构规划时,留意遵从以下准则:

(1)外围VDD、VSS走线尽或许宽,减小走线上的电阻;(2)规划一种 VDD-VSS之间的电压箝位结构,且在产生ESD时能供给VDD-VSS直接低阻抗电流泄放通道。关于面积较大的电路,最好在芯片的四周各放置一个这样的结构,若有或许,在芯片外围放置多个VDD、VSS的PAD,也能够增强全体电路的抗ESD才能;(3)外围维护结构的电源及地的走线尽量与内部走线分隔,外围ESD维护结构尽量做到均匀规划,防止地图规划上呈现ESD薄弱环节;(4)ESD维护结构的规划要在电路的ESD功用、芯片面积、维护结构对电路特性的影响如输入信号完整性、电路速度、输出驱动才能等进行平衡考虑规划,还需求考虑工艺的容差,使电路规划到达最优化;(5)在实践规划的一些电路中,有时没有直接的VDD-VSS电压箝位维护结构,此刻,VDD-VSS之间的电压箝位及ESD电流泄放首要使用全芯片整个电路的阱与衬底的触摸空间。所以在外围电路要尽或许多地添加阱与衬底的触摸,且N+P+的距离共同。若有空间,则最好在VDD、VSS的PAD周围及四周添加VDD-VSS电压箝位维护结构,这样不只增强了VDD-VSS形式下的抗ESD才能,也增强了I/O-I/O形式下的抗ESD才能。

一般只需有了上述的大致准则,在与芯片面积折中的考虑下,一般亚微米CMOS电路的抗ESD电压可到达2500V以上,现已能够满意商用民品电路规划的ESD牢靠性要求。

关于深亚微米超大规划CMOS%&&&&&%的ESD结构规划,惯例的ESD维护结构一般不再运用了,一般大多是深亚微米工艺的Foundry生产线都有自己外围规范的ESD结构供给,有严厉规范的ESD结构规划规矩等,规划师只需调用其结构就能够了,这可使芯片规划师把更多精力放在电路自身的功用、功用等方面的规划。