有人常常这么说不论新的fpga怎样改变,其实fpga工程师学习永久便是协议,界说。其实说白了,任何接口协议都是工程师有必要了解。

zynq的渠道推出最大的协议便是axi4的协议,包括axi4-full,axi4-lite,axi4-stream。三种协议内容。

其实axi4-full比axi4-lite最大的差异,axi4-full支撑的位宽更宽,而且支撑brust突发形式。而axi4-stream,便是没有地址信号,地址相关握手信息,

关于axi4-full编写代码,一般来说首要做好地址握手,然后再做数据握手,有人必定问会不会一起。一般来说,及时一起地址和数据,地址也是优先形式,然后再数据。发送端能够等候确认。

然后关于axi4-stream,只要tdata信号,在许多pcie,srio,xaui的高速接口协议中,常常运用axi4-stream的协议。这个时分axi4-stream的vaild的第一次有用数据都是数据格式头部。接纳ready信号握手valid的信号。

axi4-stream-slave 接纳数据形式如下.

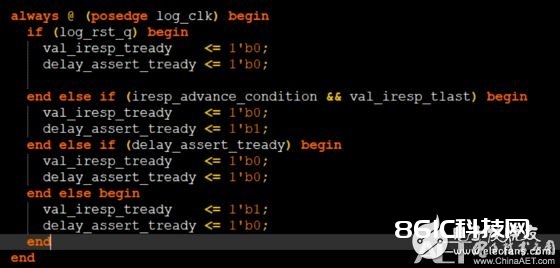

xilinx官方实例代码如下,其实大约意思便是一个高电平之后,变成低电平。然后再高电平,等候tlast信号再拉低。这样做的为了时序紧凑型,xilinx为了方便在第一个valid和ready信号得到头部信号,这个有个时间短的停留时间去剖析头部数据。

当然你能够写成状态机形式,上面代码,说实在我看得头疼。等候valid,输出一次高电平,然后得到头部数据,再拉低数据,然后再输出高电平得到数据段数据。最终依据last信号完毕ready信号。

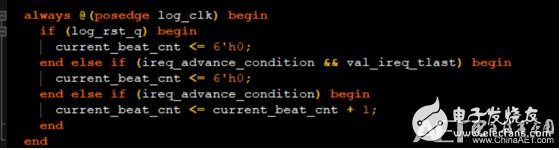

关于发送数据来说。xilinx官方运用一个脉冲计算器来tdata数据切换不同的数据内容

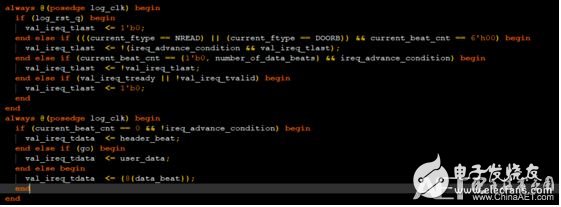

tlast信号,运用不同形式,输出不同的值,不过都是高电平一次,然后变低信号。tdata依据不同的长度来切换数据内容。

这个代码我也看得头痛,其实也能够用状态机编写,首要是输出一个头部,然后等候一次,再输出额定的数据,在最终一个数据段,输出last信号。