1、 引 言

现代电子体系规划中,数字体系规划所占的份额越来越大,数字化、集成化是未来体系开展的趋势;CPLD/FPGA作为可编程ASIC器材,将在数字逻辑体系规划中发挥越来越重要的效果。在数字通讯范畴,软件无线电在数字通讯中,特别是第3代移动通讯中的使用越来越成为研讨的焦点,欧洲的ACIS(先进的通讯技能与事务)方案,美国的多频带宽式手机与基站体系规划等都将着眼点放在依据软件无线电的第3代移动通讯体系上。一起,软件无线电技能与计算机技能交融,也为第3代移动通讯体系供给了杰出的渠道。在实践的数字通讯体系中,数字基带传输在使用上虽不如频带传输广泛,但仍有相当多的使用规模。重要的是,数字基带传输的基本理论不只适用于基带传输,并且还适用于频带传输。本文针对数字基带通讯体系中广为使用的AMI码,选用依据FPGA在Max+plusII渠道上进行规划与完成。

2 、AMI编码器VHDL规划

2.1 AMI码的规划

实践的基带传输体系,含有丰厚直流和低频成分的基带信号不适宜在信道中传输。而对具有易获取守时信息、无直流成分和只要很小的低频成分、以及具有内涵纠错才能的信号才适宜在基带传输体系中传输。AMI码、HDB3码均具有这些特色,因而广泛使用。

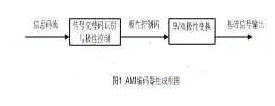

AMI码编码规矩:代码中的0仍为传输码0,而把代码中的1替换地变为传输码的+1-1+1-1,…。据AMI码的编码规矩和特色,在对它进行建模时,因为体系是依据CPLD/FPGA构成的模块,其输入、输出信号为TTL电平,即为单极性信号,而AMI码信号为双极性归零信号,而HDB3编码输出相似,因而须将输入的单极性信号转化成输出的双极性信号。为完成AMI编码功用,需将软、硬件混合规划,其功用模块分为两大部分,一部分通过VHDL言语建模和编程完成;另一部分通过由单/双极性改换电路来完成。AMI编码器组成框图如图1。

图1的第一个方框的功用表明传号(即信码“1”)替换代码辨认与极性操控,依据编码规矩,代码中的0以为传输码0,而把代码中的1替换地交换为+1和-1(或-1和+1)。考虑到+1和-1不能直接通过FPGA/CPLD来完成,而是通过外围的单/双极性改换电路来完成,因而,首要树立辨认符号来替代+1、-1和0。按此建模思维,可得到单/双极性操控的功用如表1。

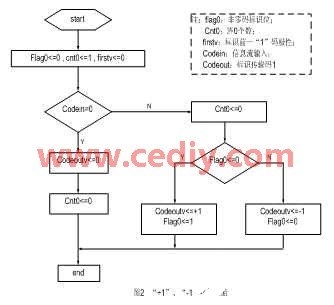

在编码过程中要考虑的问题是,怎么把音讯码中的0变为操控码“00” ;把音讯码中的1替换的变为操控码“01”和“10” 。详细规划思路:树立一个功用模块电路,当输入为0时,数据挑选器输出为“00”,当输入为1时,设置一个偶数计数器记载1的个数,当计数器记数为偶数,使数据挑选器输出为“10”(或“01”),若计数器记数为奇数,则使数据挑选器输出为“01”(或“10”)。

2.2 AMI编码器的完成流程图

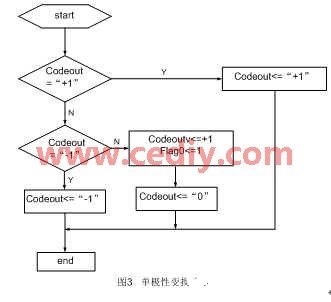

依据“+1” 、“-1”的极性判别并通过给外围的单/双极性改换电路S2(4) 、S1(4) 、S0(4)的赋值来输出0、-1、+1。

在程序输入结束并编译通过的情况下,挑选图形修改并在修改区输入程序实体名,就能够呈现程序实体框图如图4,此图看起来就像一个黑箱子,在外观上只要简略的输入、输出端口。双击此图形,便能够呈现最开端输入的程序。这个图形完成的功用和程序完成的相同,它能够下载到CPLD的试验箱的硬件设备上,从硬件效果上可看到试验效果。

2.3 AMI编码器的仿真成果与剖析

仿真波形终究的输出成果“codeout”并不是“0”、“+1”、或“-1”的多电平改动的波形,它实践上是一组地址操控码,在极性转化电路中选中不同的通道,即可完成单极性到双极性的转化。图5是一路信码通过(原码输入codein:100001000011000011000010)正、负替换编码改换后终究的输出波形仿真。依据AMI编码准则主要是将信号输入码流中的非零码转化成替换的“+1”和“-1”码,而其间的0码不变。

由图5可知:codeout0表明“-1” 码波形,codeout0由codeoutv1.Q和codeoutv2.Q的波形叠加而成。当codeoutv1.Q和codeoutv2.Q同为高电平时,codeout0输出为“ –1” 码,显现为高电平,不然输出为0,显现为低电平; codeout1表明“+1”码波形,codeout1由codeoutb1.Q和codeoutb2.Q的波形叠加而成。当codeoutb1.Q和codeoutb2.Q同为高电平时,codeout1输出为“+1” 码,显现为高电平,不然输出为0,显现为低电平;codeout用三位二进制码表明AMI码的编码成果(“0”表明原信号的“0” 码,其间1码表明“-1” ,其间2码表明“+1”)。但在编码过程中,因为基带传输体系都是从接收到的基带信号中提取位同步信号,而位同步信号却又依赖于代码的码型,假如代码呈现长期的连 “0” 符号,则基带信号中长期呈现 0 电位,从而使位同步康复体系难以确保位同步信号的准确性,发生的成果是编码器输出成果终究促进正、负改换过程中触发沿改动,使“-1” 、“+1”的极性过错地改动。

3、 AMI译码器的VHDL规划

3.1 AMI译码器规划准则

AMI码译码原理:把输入的音讯码流中的非零码转化成替换呈现的+1和-1码,而0码不变。在译码过程中要考虑的问题是,怎么把音讯码中的“00”变为操控码0;把音讯码中的替换的“01”和“10”变为操控码1。详细建模思路:树立一个功用模块电路,当检测到“00”时,数据挑选器输出为0,当输入为“10”或“01” 时,使数据挑选器均输出为1。输出成果中1码没有正、负性的区别。

3.2 AMI译码器的仿真成果与剖析

图6中zb是含有“+1”的输入码流: +1000000000+100000+100000;fb是含有“-1”的输入码流—-00000-100000-100000-100000;clk是表明时钟输入;V2、V3表明时钟信号的提取;decode表明译码输出:1000010000110000110000。Zb和fb在orl功用器材(即加法器)的效果下叠加而成decode。功用元件zv和fv检测到非“+1” 、“-1”的正信号就输入为0。

整个体系程序编译成功后,能够创立顶层文件,生成下载编程文件,进行程序下载到可编程器件中。

4 、结 论

现代通讯体系的开展跟着VHDL的规划性言语的呈现和ASIC的使用进入了一个新的阶段,特别是,对数字通讯体系的ASIC芯片的研讨为现代通讯体系的规划有着重要的实践性含义。本文作者立异点在于针对数字基带传输体系中AMI码的特色,选用依据CPLD/FPGA的VHDL言语,仿真完成了AMI的编码器和译码器。仿真成果表明,选用依据FPGA的AMI码的规划有用、便利、简略易行。

责任修改:gt