ADCLK946相关信息来自ADI官网,详细参数以官网发布为准,ADCLK946供给信息可在查IC网查找相关供给商。

产品概况

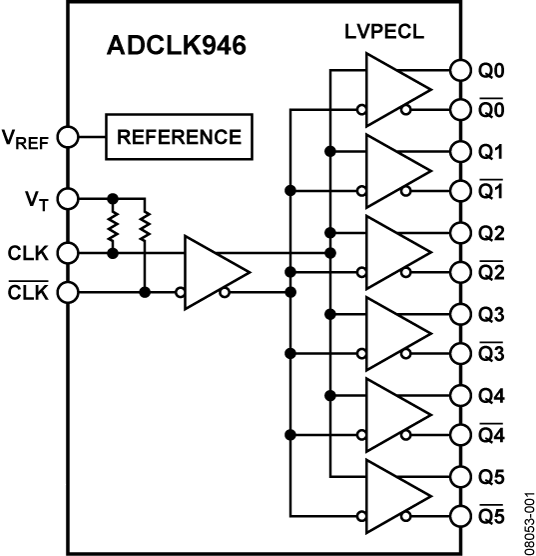

ADCLK946是一款选用ADI公司专有的XFCB3硅锗(SiGe)双极性工艺制作的超快型时钟扇出缓冲器。这款器材规划用于要求低颤动功能的高速使用。

这款器材具有一个带中心抽头、差分、100 Ω片上端接电阻的差分输入。支撑直流耦合LVPECL、CML和3.3 V CMOS(单端)和沟通耦合1.8 V CMOS、LVDS和LVPECL输入。VREF引脚可用来为沟通耦合输入供给偏置。

ADCLK946具有六个全摆幅的发射极耦合逻辑(ECL)输出驱动器。关于LVPECL(正ECL)输出,将VCC偏置到正电源, VEE偏置到地。关于ECL输出,将VCC偏置到地,VEE偏置到负电源。

ECL输出级规划成将每端800 mV直接驱动至端接于VCC至2 V的50 Ω电阻,然后取得1.6 V的总差分输出摆幅。

ADCLK946选用24引脚LFCSP封装,额外作业温度规模为−40℃至+85℃的规范工业温度规模。

使用

优势和特色

|

|

ADCLK946电路图

ADCLK946中文PDF下载地址

ADCLK946下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/ADCLK946.pdf